Critical Embedded Systems based on AI

# D4.1 Interim Platform Technologies Report

Version 1.0

#### **Documentation Information**

| Contract Number            | 101069595                                                              |

|----------------------------|------------------------------------------------------------------------|

| Project Website            | www.safexplain.eu                                                      |

| Contratual Deadline        | 31.03.2024                                                             |

| <b>Dissemination Level</b> | PU                                                                     |

| Nature                     | R                                                                      |

| Authors                    | Enrico Mezzetti (BSC), William Guarienti (EXI)                         |

| Contributors               | Mikel Fernandez (BSC), Sergi Vilardell (BSC), Francisco Cazorla (BSC)  |

| Reviewer                   | Gabriele Giordana (AIKO)                                               |

| Keywords                   | Platform support, Hardware and Software stack, Timing characterization |

This project has received funding from the European Union's Horizon Europe programme under grant agreement number 101069595.

# Change Log

| Version | Description Change |

|---------|--------------------|

| V0.1    | First draft        |

| V0.2    | Reviewed version   |

| V1.0    | Final version      |

# **Table of Contents**

| E | xecu | tive Summary3                                         |

|---|------|-------------------------------------------------------|

| 1 | Ir   | ntroduction4                                          |

|   | 1.1  | Scope4                                                |

|   | 1.2  | Structure of the Document5                            |

| 2 | Ν    | IVIDIA ORIN MPSoC                                     |

|   | 2.1  | Orin overview6                                        |

|   | 2.2  | Default software stack7                               |

| 3 | T    | iming Interference Control (T4.1)9                    |

|   | 3.1  | Software Sources of Timing Interference9              |

|   | 3.2  | Hardware Sources of Timing Interference12             |

|   | 3.3  | Technological assessment22                            |

| 4 | 0    | bservability Channels (T4.2)24                        |

|   | 4.1  | PMU and HEM analysis24                                |

|   | 4.2  | HEMs identification25                                 |

|   | 4.3  | Hardware Event Monitors PMULib29                      |

|   | 4.4  | SCF HEMs overhead                                     |

|   | 4.5  | Technological assessment                              |

| 5 | Т    | iming Prediction Methods and Tools (T4.3)35           |

|   | 5.1  | Timing characterization strategy35                    |

|   | 5.2  | Inter-Run Variability35                               |

|   | 5.3  | Statistical Analysis based on the Markov Inequality40 |

|   | 5.4  | Interference monitoring mechanism and Templates42     |

|   | 5.5  | Technological assessment44                            |

| 6 | Ρ    | latform- and System-level V&V support (T4.4)48        |

|   | 6.1  | SAFEXPLAIN Middleware concept48                       |

|   | 6.2  | SAFEXPLAIN Middleware support49                       |

|   | 6.3  | Technological assessment53                            |

| 7 | A    | cronyms and Abbreviations                             |

| 8 | R    | eferences                                             |

| 9 | A    | nnex 1 – PMULib interface                             |

|   | 9.1  | Function Documentation58                              |

|   | 9.2  | Macro Documentation60                                 |

|   | 9.3  | Usage Example63                                       |

# **Executive Summary**

This deliverable reports on the technical and technological progresses achieved in WP4 during the first 18 months (MS2) of the project. In particular, this report captures the advancements done in all WP4 tasks (T4.1-T4.4) by MS2 hence covering aspects related to hardware and timing characterization as well as specific solutions adopted at platform level to support the activities of other work packages. In the following we provide an assessment of the degree of completion in each of the WP4 tasks and the respective outcomes (technologies and tools). Technologies and tools will be also assessed with respect to their readiness for integration and next steps.

# 1 Introduction

This report reports on the progress achieved in the scope of WP4. This work package brings together all platform-level aspects that are relevant for the supporting both performance and FUSA requirements on top of the platform. The overarching goal of WP4 is to support the development, execution, and analysis of the solutions proposed by other technical work packages and deployed through SAFEXPLAIN case studies.

### 1.1 Scope

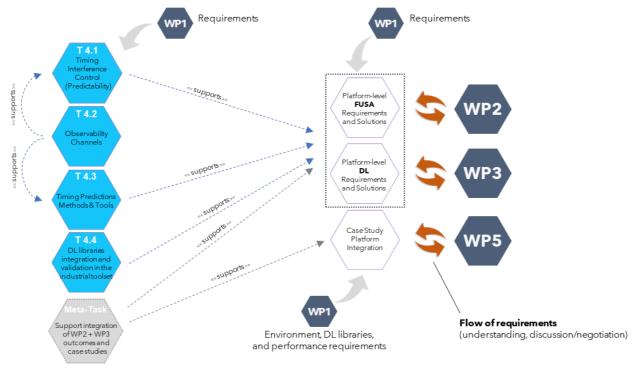

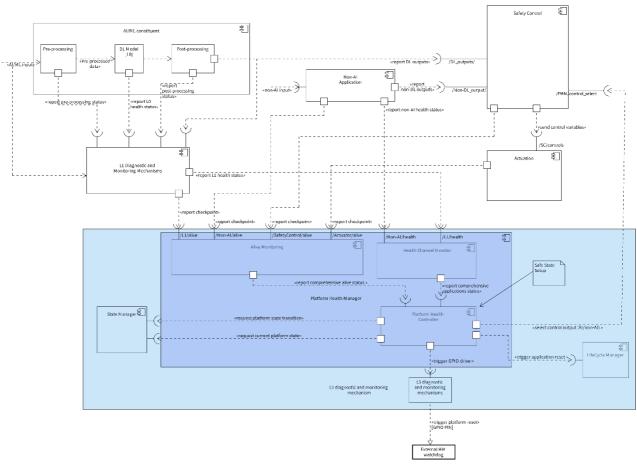

The Platform WP comprises 4 tasks and a higher-level meta-task to support the integration of WP2 and WP3 solutions in the case studies. As such, WP4 has strict relations with all SAFEXPLAIN work packages and, in fact, facilitates their alignment. Figure 1 below depicts the main tasks in WP4 and how they support SAFEXPLAIN technologies and integration by capturing explicit and implicit requirements from other WPs.

Figure 1 - WP4 role and relation with other WPs.

The main technological tasks in the WP are:

- **T4.1 Timing interference control**, covering the hardware analysis of the target platform to identify the sources of interference and the available support for segregation and partitioning. This task is critical to support FUSA aspects, and particularly the deployment, under the supervision of WP2, of FUSA architecture and patterns presented in [1].

- **T4.2** Observability channels, dealing with available means of collecting hardware-level information on program execution on top of the target platform, and providing an

integrated tool to configure those means and access extract the relevant information at both run and analysis time.

- **T4.3 Timing prediction methods and Tools**, providing support for the analysis of the timing behavior of the deployed functionalities, building on timing interference mitigations enabled by T4.1 analysis and SAFEXPLAIN FUSA solutions (WP2) and exploiting timing information gathered on top of T4.2 outcomes.

- **T4.4 DL libraries integration and validation in the industrial toolset**, facilitating the integration of SAFEXPLAIN DL libraries and solutions in a partially automated setup supporting FUSA task through offline V&V activities and run-time monitoring.

### 1.2 Structure of the Document

In the following sections we provide a review of WP4 activities and progresses up to MS2.

- We will start with a section devoted to the introduction to the NVIDIA AGX Orin [2], the reference platform adopted in SAFEXPLAN. This covers both hardware and software aspects.

- We will then continue following the task structure of the WP.

Each section will include a description of the task objectives, the strategy followed, the obtained results, and an assessment over maturity of the provided solutions from the standpoint of the integration on the case studies.

# 2 NVIDIA ORIN MPSoC

One of the main objectives of WP1 consisted in the selection of the relevant target boards for the project. The selection process aimed to identify target platforms that were both representative of the target domains (critical embedded systems) and therefore interesting from the FUSA perspective, and apt to sustain the execution of performance intensive AI-based applications, hence providing support for general-purpose and AI-specific hardware accelerators.

Based on the technological and performance requirements emerging form the use cases, the project partners reached a consensus on the adoption of the NVIDIA AGX Orin [2] as target platform.

In the following we summarize the main hardware features relevant for the project. We also report on the adopted software stack, which is equally relevant to provide a homogeneous development and execution environment across project partners and tools.

### 2.1 Orin overview

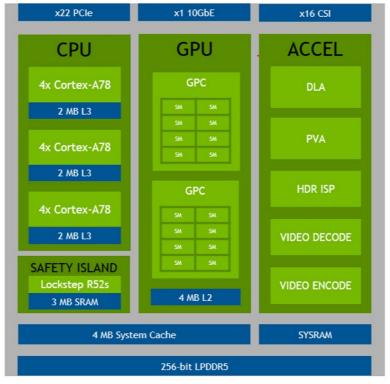

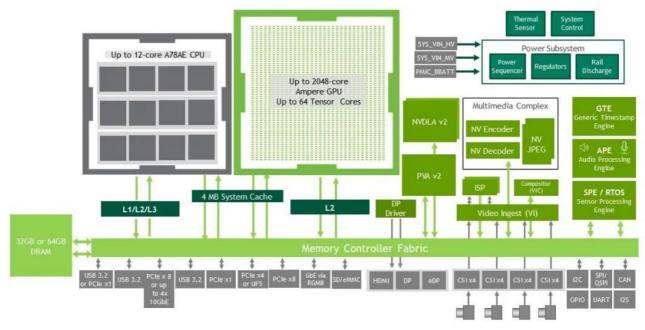

The NVIDIA Jetson AGX Orin is a family of heterogenous MPSoC (Orin 32/64 Nano) developed by NVIDIA to cover the emerging requirements form diverse markets, all sharing the need for high-performance to support AI-based functionalities at reduced SWaP (Size, Weight, and Power). In SAFEXPLAIN, the AGX Orin Dev Kit has been selected.

The Orin comprises 3 clusters of 4 Arm Cortex-A78AE CPUs [3], a NVIDIA Ampere GPU, ad-hoc Aloriented accelerator such as NVDLA and PVA, as well as a video encoder and a video decoder (see Figure 2). The system also exploits a high-speed IO, with 204 GB/s of memory bandwidth, and 32GB of DRAM (in the Dev Kit version). The Orin can deliver up to 275 TOPS which are enabling the execution of multiple concurrent AI application.

Figure 2 - Block Diagram of our target platform (from [4]).

### 2.2 Default software stack

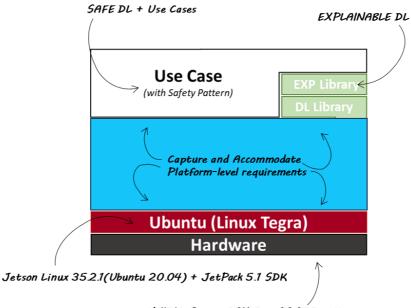

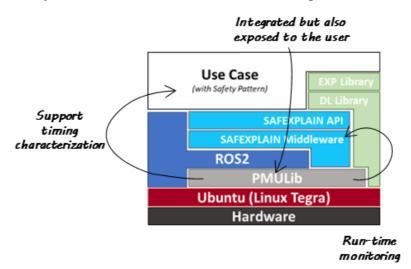

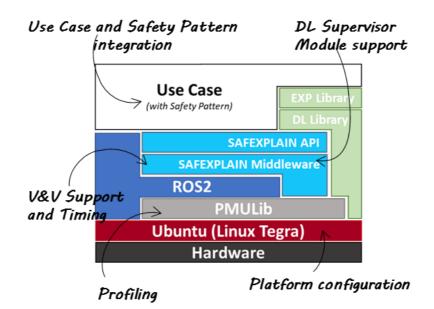

The NVIDIA AGX Orin [2] comes with tailored OS support and libraries. The software stack includes a specific version of a Linux-based Operating System as well as a score of dedicated libraries to support the development and execution of AI applications. To favour homogenization and coordination across development environments in the different WPs, WP4 promoted the early identification of a shared software stack configuration to guarantee inter-compatibility of tools. Figure 3 illustrates the positioning of the low-level software layer in the SAFEXPLAIN stack.

NVIDIA Jetson AGX Orin 32GB Dev Kit

Figure 3 - Baseline HW and SW stack.

As anticipated the low-level software stack includes a tailored instance of an Ubuntu release also called Linux Tegra version. The set of tools normally available on Linux systems is complemented by the NVIDIA proprietary SDK JetPack, providing the necessary support to exploit the programming of the GPU and accelerators and the exploitation of standard deep learning libraries. Technological solutions developed in WP2 and WP3 are meant to rely on this software substrate. The setup is also the baseline for the development and porting of the different case studies.

Current SAFEXPLAIN setup consists in the following elements and versions:

| • | Jetpack | 5.1 |

|---|---------|-----|

|   |         |     |

- Jetson Linux 35.2.1

- Ubuntu Version 20.04

- Kernel Version 5.10.65-tegra

- Tensor RT 8.5.2

- cuDNN 8.6.0

- CUDA 11.4.19

- OpenCV 4.5.4

- Python 3.8.10

- PyTorch 1.14

- Vulcan 1.3.203

- Vulcan SC 1.0

Changes to the setup are expected to happen during the project, only after checking the compatibility of the updates with the partners assumptions. We expect to move to the new release of the Jetson Linux and JetPack later this year (the new version is still under beta release).

# 3 Timing Interference Control (T4.1)

This task analyses and classifies the sources of timing interferences, and the hardware/software mechanisms available to control such interference (e.g., cache partitioning). Then, it uses those mechanisms to limit timing interference by construction, especially for DL-based tasks, as part of the SAFEXPLAIN software stack, so they can be used in the case studies, and allow implementing the 'containers' described in T2.4. Timing interference analysis strategy, including analysis time and run-time interference mitigation and control approaches, are designed, and developed in alignment with WP2 strategy [1]. At the top level we classify the sources of timing interference between software (Section 3.1) and hardware (Section 3.2).

### 3.1 Software Sources of Timing Interference

The Orin software stack builds on Linux Tegra, which consists in the tailoring of a full Ubuntu distribution. The use of a Linux-based, general-purpose operating system introduces some interference or jitter in the execution of tasks stemming from the many background activities the OS is undergoing. This would not be the case in real-time operating systems where OS services are limited, and timing of user applications is preserved. Real-time OSes, however, are not available on the target platform.

### 3.1.1 Linux Ubuntu setup

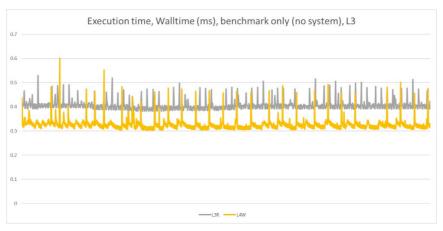

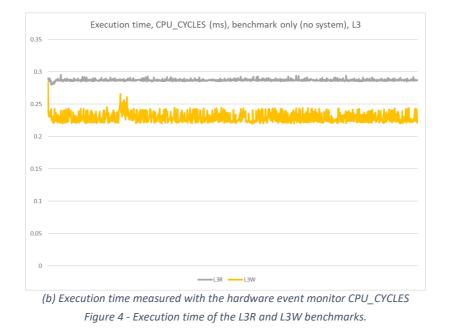

We start our analysis by running several reference benchmarks on the default Orin software-stack, only including the Linux layer. Selected benchmarks consist in carefully designed pieces of code exercising configurable large amount of a specific type of data accesses (read or write operations) to a specific layer in the cache and memory hierarchy (L2, L3 L4, or main memory). We tracked the wall-clock time and the cycle count. Figure 4 shows the results for a benchmark performing reads to the L3 (L3R) and the benchmark performing writes to the L3 (L3W).

Figure 4a shows that every 15 to 30ms approximately the wall clock time suffers a spike. This behavior can be most clearly observed for the L4W benchmark. This relates to activities of the Linux OS that are triggered periodically. Figure 4b shows that those peaks do not arise when we measure the actual execution time of the task, i.e. the time it was actually running in the CPU: as it can be seen the peaks disappear. This confirms that the peaks are due to the OS activity.

(a) Execution time measured as the Wall clock time using clock\_gettime().

#### D 4.1 Interim Platform Technologies Report Version 1.0

We extended the analysis to other benchmarks performing reads and writes to the different levels of the memory hierarchy (L2, L3, and memory). For each of them, we perform a comparison between the wall time and the clock time as reported by the CPU\_CYCLES counter. We identify that the wall clock time is approximately 40% higher than the time reported by CPU\_CYCLES, due to activities performed by the OS.

|      | Ratio<br>(avg) |

|------|----------------|

| L2R  | 1.45           |

| L2W  | 1.48           |

| L3R  | 1.41           |

| L3W  | 1.46           |

| L4R  | 1.38           |

| L4W  | 1.38           |

| MEMR | 1.34           |

| MEMW | 1.36           |

These results confirm the existence of OS activities that can affect the execution time of running programs and hence need to be removed.

### 3.1.2 ROS2 setup

The Robotic Operating System (ROS) is the de-facto standard for developing complex autonomous systems characterized by a strong interaction with the physical environment. ROS, which underwent through a major release and is now available in version 2 (aka ROS2), is also typically used as a middleware layer in AI-based applications in several domains. ROS2 [5] provides a relatively simple and scalable application semantics based on communication among functional nodes that cooperates to deploy a given functionality, from sensers to actuators. The communication semantics is based on the publisher-subscriber paradigm.

SAFE

In the scope of SAFEXPLAIN, ROS2 has been selected as a baseline element in the software stack as all use cases clearly fit its publisher-subscriber semantics. More details on SAFEXPLAIN software stack, and how ROS2 fits in it, are provide and discussed in Section 6.1.

ROS2 contributes an additional software layer that can introduce further jitter on top of the OS-induced one.

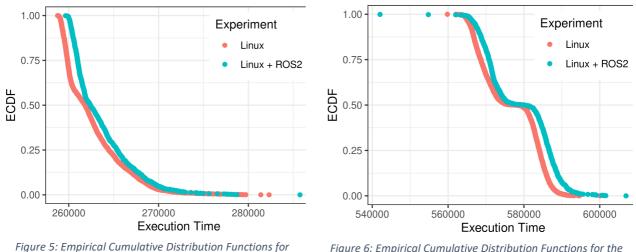

We assessed the overheads introduced by ROS2 on top of those introduced by Linux. To that end we ported the benchmarks as ROS2 nodes and executed them, measuring CPU\_CYCLES. We Compared the resulting distributions of two benchmarks, L2R and L3R.

In Figure 5 and Figure 6 we see that the shape of the distribution of execution for both experiments done with Linux and with Linux + ROS2 are very similar. ROS2 seems to add some overhead to the overall execution time, which is relatively small, about a 0.5% increase in the distribution mean in both cases. Nonetheless, it does not provide additional noise to the execution time.

We can test that by compensating the overhead induced by ROS2 and comparing the distributions with a Kolmogorov-Smirnov (KS) test. The KS test uses as statistic the maximum difference in the Empirical Cumulative Distribution Function (ECDF) in this case. When performing the KS test with bootstrap resampling for a more robust estimation, the p-values are 0.40 and 0.47 for L2R and L3R respectively, therefore we cannot reject that the distributions are different.

the execution time of L2R with Linux and Linux + ROS2

Figure 6: Empirical Cumulative Distribution Functions for the execution time of L3R with Linux and Linux + ROS2

Overall we conclude that not additional means are needed to control ROS2 impact on the execution time of applications.

### 3.1.3 Custom middleware setup

For the sake of completeness, the software-level interference analysis will be completed by considering the additional layer contributed by the SAFEXPLAIN Middleware, which is an abstraction layer we developed to accommodate various project level aspects, as detailed in Section 6.1. A thorough analysis is postponed to the final release of the Middleware and, hence, results will be included in the next release of this deliverable. Nonetheless, we performed some preliminary experiments on an intermediate version which seems to confirm the trend observed with ROS2. This is indeed not surprising in reason of the limited intrusiveness of the Middleware on the functional behavior, which is preserved and contained within the ROS2 entities.

### 3.2 Hardware Sources of Timing Interference

A high-level view of the Orin block diagram, showing the main clusters and devices, is provided in Figure 7) from the official documentation [2].

Figure 7 - Orin high-level block diagram (from [2]).

### 3.2.1 CPU Complex

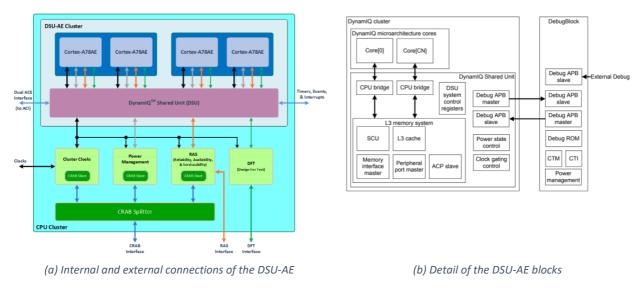

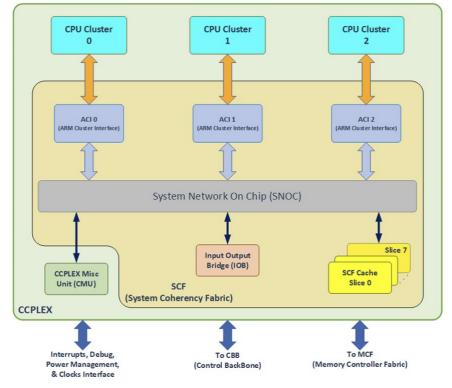

The high-level overview of the CPU Complex showing its CPU cores is presented in **Error! Reference source not found.Error! Reference source not found.** We can see three different CPU clusters, each one implementing four Cortex-A78AE cores and a cluster-private L3 cache that is shared among the cores of each cluster.

#### 3.2.1.1.1 DynamIQ<sup>™</sup> Shared Unit (DSU-AE)

Each cluster in the CPU Complex comprises the DynamIQ Shared Unit (DSU-AE) that embeds a 2-MiB L3 Cache and the Snoop Control Unit (SCU), as seen in Figure 9b. The L3 and SCU are in charge of maintaining coherency between caches in the cores and L3. So, while the caches in the cores are private, the L3 is shared among the 4 cores in the cluster.

The DSU-AE provides the internal interfaces to the cores, as presented in Figure 9a where the connection to the four cores can be observed.

Figure 8 - Block diagram of the CPU Complex (from [2]).

Figure 9 – Block diagrams of the DSU-AE [6]

#### Comparators

Comparator logic is only enabled when the Cortex<sup>®</sup>-A78AE is operating in Lock-mode. There are two instances of each comparator, reporting on separate outputs. Delay flops are also associated with Lock-mode. The delay flops create the temporal diversity between the primary and redundant logic and align the comparison logic.

#### **Snoop Control Unit (SCU)**

The SCU contains buffers that can handle direct cache-to-cache transfers between cores without having to read or write data to the L3 cache. Cache line migration enables dirty cache lines to be

moved between cores, and there is no requirement to write back transferred cache line data to the L3 cache.

#### L3 cache

The cache is 16-way set associative with a 64-byte line length and a total size of 2MB. It is shared by all the cores in the cluster and supports stashing request from the ACE/CHI interface. However, if it is heavily loaded and does not have any free buffers, it drops the stash request.

The L3 cache data allocation policy changes depending on the pattern of data usage. Exclusive allocation is used when data is allocated in only one core. Inclusive allocation is used when data is shared between cores. The L3 cache implements two slices, each with a set of tag and data RAMs. Requests are allocated to a particular slice based on the address of the request. Splitting the cache into slices improves the bandwidth because the two slices can be accessed in parallel.

| Cache capacity | Tag RAM | Data RAM |     |     |     |     |  |

|----------------|---------|----------|-----|-----|-----|-----|--|

|                | 0       | 1        | 2   | 3   | 0   | 1   |  |

| None           | Off     |          |     |     | Off |     |  |

| 1⁄4            | On      | Off      |     |     | On  | Off |  |

| 1/2            | On      |          | Off |     | On  | Off |  |

| 3⁄4            | On      |          |     | Off | On  |     |  |

| All on         | On      |          |     |     | On  |     |  |

The L3 supports the creation of groups of cache ways to partition and assign to individual processes. Cache partitioning ensures that processes do not dominate the use of the cache to disadvantage other processes.

L3 cache partitioning is achieved by partition scheme IDs and groups of cache ways, where:

- Each group contains four ways.

- Each group can either be assigned as private to one or more partition scheme IDs, or be left unassigned.

- Each unassigned group can be shared between all eight partition scheme IDs.

Each core in the cluster must be assigned to at least one of the eight partition scheme IDs. L3 cache accesses from a given core can allocate into:

- Any cache way that belongs to a group that is assigned as private to the partition scheme ID of this core.

- Any cache way that belongs to an unassigned group that is shared by the entire cluster.

#### L3 cache placement

The placement algorithm used for the L3 is undocumented. BSC investigated to empirically determine how data is placed into L3 sets. There are two main assumptions that were investigated:

- Modulo placement

- XOR placement, similar to the one used in the Cortex-A78AE L2 cache.

BSC prepared an experimental setup where, based on the initial assumption, more than 16 pieces of data would be placed into a single L3 set. If the assumption was correct, we would observe L3 cache misses, as the L3 only provides 16-ways per cache set.

The result showed that the formula used for determining the L3 set for placement is ([26:17] XOR [16:7]). Bits [5:0] are within the cache line offset (64 bytes) while bit 6 is used to select L3 cache slice. Figure 10 shows how memory address bits are used to access a cache lines in L2 and L3.

| address | 32 | 31 | 30 | 29 | 28 | 27 | 26 | 25               | 24           | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16  | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4    | 3    | 2  | 1 ( | ) |

|---------|----|----|----|----|----|----|----|------------------|--------------|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|---|---|---|---|---|------|------|----|-----|---|

|         |    |    |    |    |    |    |    |                  | L3 placement |    |    |    |    |    |    |    |     |    |    |    |    |    |    |   |   |   |   |   |      |      |    |     |   |

|         |    |    |    |    |    |    |    | L3XORH L3XORL    |              |    |    |    |    |    |    |    |     |    |    |    |    |    |    |   |   |   |   |   |      |      |    |     |   |

|         |    |    |    |    |    |    |    | L2 placement     |              |    |    |    |    |    |    |    |     |    |    |    |    |    |    |   |   |   |   |   |      |      |    |     |   |

|         |    |    |    |    |    |    |    | XOR high XOR low |              |    |    |    |    |    |    |    |     |    |    |    |    |    |    |   |   |   |   |   |      |      |    |     |   |

|         |    |    |    |    |    |    |    | 20               |              |    |    |    |    |    | OS | р  | age | È  |    |    |    |    |    |   |   |   |   |   |      |      |    |     |   |

|         |    |    |    |    |    |    |    |                  |              |    |    |    |    |    |    |    |     |    |    |    |    |    |    |   |   |   |   | S | lice | e+li | ne |     | ĺ |

|         |    |    |    |    |    |    |    |                  |              |    |    |    |    |    |    |    |     |    |    |    |    |    |    |   |   |   |   |   |      | lin  | е  |     | ĺ |

Figure 10 – Address bits used for L2 and L3 cache placement.

### 3.2.2 GPU Cluster

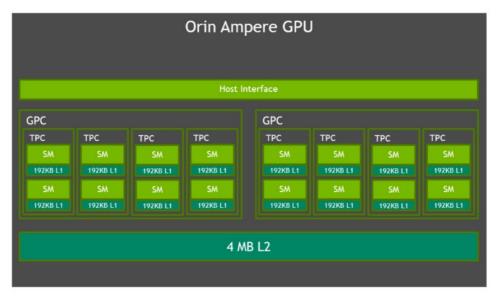

The Orin SoC has an NVIDIA Ampere GPU with two Graphics Processing Clusters (GPCs). A GPC is the high-level hardware block with all the compute/graphics processing units for graphics-related computation, rasterization, rendering, Ray Tracing, pixel generation, etc. A high-level block diagram view is presented in Figure 11.

Figure 11 – Orin Ampere GPU high level block diagram (from [2])

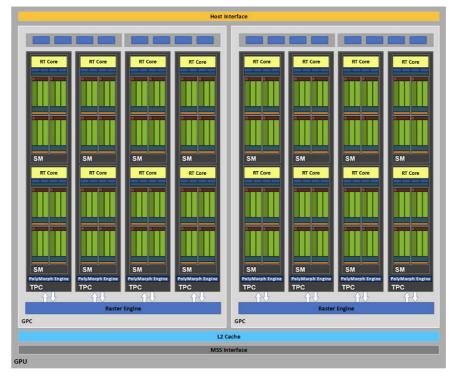

The Ampere GPC contains the following components: A Raster Engine, four Texture Processing Clusters (TPCs), each consisting of 2 Streaming Multiprocessors (SMs), each with its own Ray Tracing (RT) core, and 1 PolyMorph Engine (PE). These elements can be seen in Figure 12.

#### D 4.1 Interim Platform Technologies Report Version 1.0

# SAFEXPL

Figure 12 – Orin Ampere GPU detailed block diagram (from [2]).

#### **Streaming Multiprocessor**

The Ampere Streaming Multiprocessor has 128 CUDA cores. As shown in Figure 13, the SM is partitioned in four processing blocks, with each containing:

- 1 3rd-generation Tensor core,

- 1 64-KiB Register Files (in 16,384 x 32 organization),

- 1 Texture (TEX) unit,

- 1 L0 I-Cache, 1 Warp Scheduler, and

- 1 Dispatch (32 threads/clk) unit,

and all four sharing:

- 1 192-KiB for L1 Data Cache and Shared Memory, and

- 1 2nd-generation Ray Tracing (RT) core.

#### 3.2.3 Interconnect

The interconnect is based on 2 technologies based on the AMBA protocol of ARM: AXI3 and AXI4. The system control fabric is based on AXI3, this means no QOS protocol is applied on them. On the other hand, the data fabric to access main memory (DDR) is based on AXI4 protocol.

### 3.2.4 Other features

The board is also equipped with a series of clusters focused on special tasks that are configured by Nvidia on their firmware. Those modules are: SPE Sensor processing engine; APE Audio processing engine; Safety Island in charge of the power control of the board; Boot power management; Real time cameras processing.

Figure 13 – Ampere Streaming Multiprocessor block diagram (from [2])

#### 3.2.4.1 Input / Output (I/O)

#### GPC-DMA

There are 32 channels in GPC-DMA. A DMA channel can transfer a specified range of data between a memory address space (SysRAM or external memory) and an MMIO address space. A DMA channel can also transfer data between a memory address space and another memory address space (Mem-to-Mem copy). The DMA controller follows a simple round robin arbitration scheme between the channels, starting with channel 0. Each channel can have an independent burst transfer size programmed to one word, two words, four words, eight words, or 16 words. For Memory transfers, we only support two-words and 16-words bursts. There is a corresponding read/write buffer in the memory buffer manager for each channel. There is also a corresponding buffer for each channel on the peripheral side.

#### **Continuous Mode**

In continuous mode single buffer mode, software has two separate buffers that are maintained by software to emulate the hardware ping pong buffer. In this mode, software enables the DMA with the ping-buffer address and then reprograms the DMA with pong buffer after enabling the DMA. The DMA registers are shadowed (latched) every time upon entering the continuous cycle. The register programming can be done for the pong buffer either after enabling the channel (for the first reprogramming) or receiving an interrupt (for any subsequent reprogramming).

#### 3.2.4.2 SCF and L4

The System Coherency Interconnect (SCF) connects the CPU Complex (CCPLEX) to the DRAM. It is in charge of maintaining coherency between the clusters and connecting them to the rest of the SoC. The SCF embeds a shared L4 cache that is shared among the three CPU clusters. The cache is also shared with the GPU, but it's not fully coherent; coherency is one-way [7], so the GPU is able to read CPU cache, but not the other way around. In Figure 14 a view of how the SCF is connected to the clusters and to the interfaces to the rest of the SoC is shown.

Figure 14 – Block diagram of the CCPLEX, including the SCF [6].

The L4 cache is set-associative and is partitioned in 8 512KB slices, for a total of 4MB. Memory requests from the CPU clusters are routed through the L4 cache and to the Memory Controller Fabric (MCF) as seen in Figure 14. Transactions to memory mapped Input/Output (MMIO) are routed through the Input Output Bridge (IOB).

### 3.2.5 Interference channel identification

In order to identify the sources of inter-process interference, BSC performed an analysis of the hardware architecture as presented in this Section. We studied possible bottlenecks in the design. We also interact with the use case providers to understand how their application uses the platform. The combination of the potential source of contention at hardware level and how the application actually uses the hardware, leads us to conclude the actual sources of contention.

#### 3.2.5.1 Domains of resource sharing

We use the term resource sharing domain or resource sharing level to categorize how applications share hardware shared resources. It is worth noting that the hardware resources that are shared among cores and may become a contention point are related mainly to the datapath to memory:

- <u>Intra CPU core</u>. Private computing resources, private first level data and instruction caches, private L2, which ultimately request data to the shared L3 on miss.

- <u>Intra CPU cluster</u>. The SCU, including the shared L3. This component includes the snoop control and and L3 shared withing the CPU Cluster.

- <u>Inter CPU cluster</u>. The SCF, including the shared L4. This component centralises accesses to memory from the three CPU Clusters and the GPU.

- <u>Accelerators</u>. Accelerators can be shared among applications. This includes the GPU and specific accelerators like the DLA.

#### 3.2.5.2 Usage of shared resources

We developed a questionnaire that we shared with the use case providers. The questionnaire included questions about the usage of shared resources in the Orin. The main conclusions from the questionnaire were the following:

- 1. End users are using 1 CPU cluster and might need to use several.

- 2. GPU is being used by one application only. Hence, the GPU is time shared and not space shared.

- 3. The accelerators are not being used and in case they are they will be time shared.

Hence our focus on the contention side goes on the intra CPU cluster and inter CPU cluster.

### 3.2.6 Empirical results

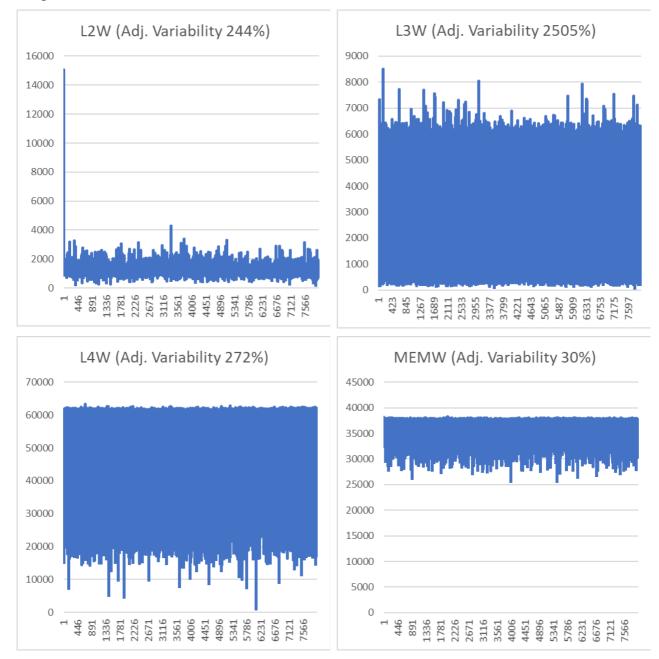

In order to empirically assess the impact of contention we develop a set of benchmarks that read/write to a given cache level. By running several of those benchmarks together we can assess whether they suffer contention in a given resource level The benchmarks are:

- L2R and L2W. Benchmarks that perform mainly reads (R) and (W) most of which hit in L2.

- L3R and L3W. Benchmarks that perform mainly reads (R) and (W) most of which hit in L3.

- L4R and L4W. Benchmarks that perform mainly reads (R) and (W) most of which hit in L4.

- MEMR and MEMW. Benchmarks that perform mainly reads (R) and (W) most of which do not hit in any cache level and go to memory.

It is noted that when a benchmark hits in a cache level it is implicitly missing the lower cache levels.

#### 3.2.6.1 L2

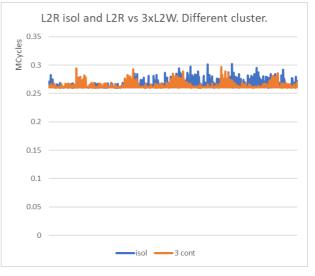

In this first experiment we run a L2R benchmark against 3 instances of the L2W benchmarks. Each benchmark executes in one of the cores of a given cluster. Figure 15**Error! Reference source not found.** below shows the execution time of the L2R benchmark. As it can be seen in Figure 15 it suffers no significant increase in the execution time when running in multicore vs when running in isolation, providing evidence that the L2 are private per core. Comparing figures Figure 15a and Figure 15b we also appreciate no difference between running all contenders in the same cluster or in a different one, due to L2 being private per core.

(a) Execution time of L2R in isolation and with contenders running on the same cluster.

Figure 15 - Execution time in ms of the L2R benchmark in isolation (blue) and contending with 3 instances of L2W (orange).

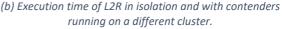

Figure 16 shows the L2 miss rate distribution for the L2R benchmark running in isolation and when with 3 contenders running L2W. It can be seen that the miss rate remains very low in both cases (mostly sub 1%), and with a very similar distribution, proving that contenders do not increase miss rate and hence that the L2 caches are private per core.

Figure 16 - Histogram with the distribution of the miss rate across different executions of L2R, in isolation (blue) and with 3 contenders running L2W (orange). This includes execution in a single cluster and in multiple clusters.

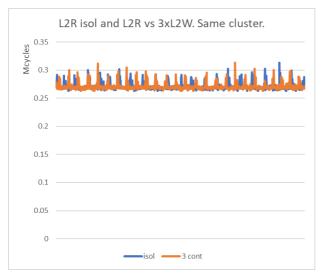

#### 3.2.6.2 L3

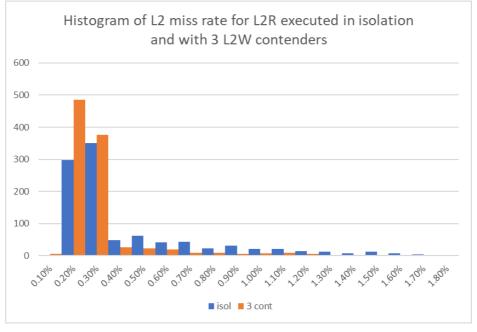

In this experiment we run a L3R benchmark against 3 instances of L3W benchmarks. Each benchmark executes in one of the cores of a given cluster. Figure 17 below shows the execution time of the L3R benchmark. As it can be seen in Figure 17b it suffers no significant increase in the execution time when running in multicore vs when running in isolation, while in Figure 17a a very significant difference can be seen. This provides evidence that the L3 are private per cluster but shared among cores within the cluster.

(a) Execution time of L3R in isolation and with contenders running on the same cluster.

(b) Execution time of L3R in isolation and with contenders running on a different cluster.

Figure 17 – Execution time in ms of the L3R benchmark in isolation (yellow) and contending with 3 instances of L3W (grey).

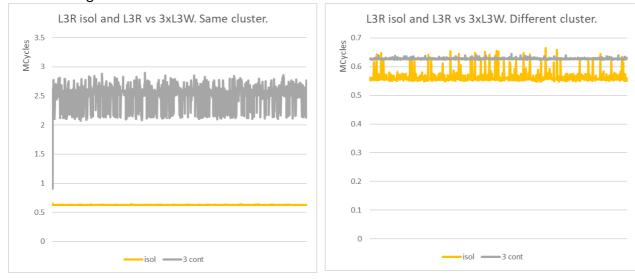

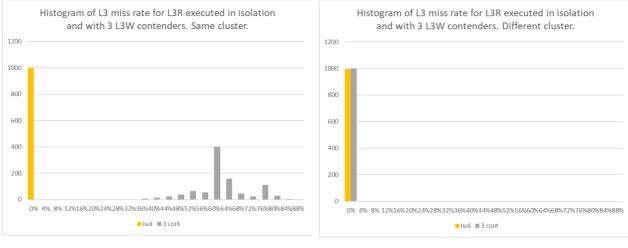

Figure 18 shows the L3 miss rate distribution for the L3R benchmark when running in isolation and with 3 contenders running L3W. In Figure 18a, it can be appreciated how multicore execution in a single cluster causes a high amount of L3 cache misses, as the contenders compete with the task under analysis for the shared L3. In Figure 18b we can see how L3 miss rate does not vary between execution in isolation and with contenders when the latter run in a different cluster, proving that the L3 is private per cluster.

(a) Execution time of L3R in isolation and with contenders running on the same cluster.

(b) Execution time of 3R in isolation and with contenders running on the different cluster.

Figure 18 – Histogram with the distribution of the miss rate across different executions of L3R, in isolation (yellow) and with 3 contenders running L3W (grey).

#### 3.2.6.3 L4

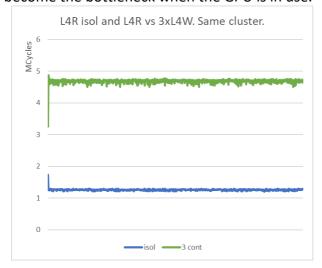

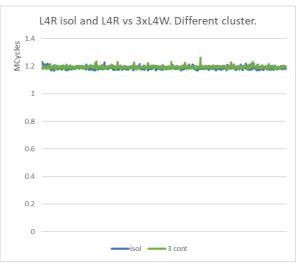

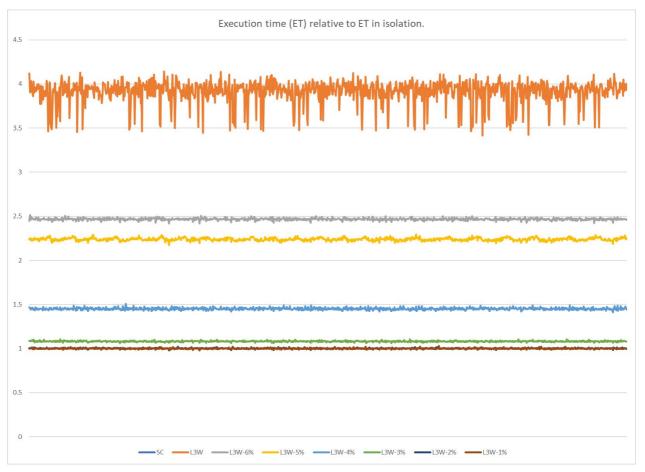

In this experiment we run a L4R benchmark against 3 instances of L4W benchmarks. Each benchmark executes in one of the cores of a given cluster. Figure 19 below shows the execution time of the L4R benchmark. As it can be seen in Figure 19b, in average the execution time is not greatly affected by multicore execution when contenders are running in a different cluster. This is due the L3 being the bottleneck in the memory hierarchy, so we only appreciate an increase in contention when running in the same cluster, as seen in Figure 19a. This is true for this scenario, where the GPU is not being used and hence the L4 cache is only used by cores, but the L4 may become the bottleneck when the GPU is in use.

(a) Execution time of L4R in isolation and with contenders running on the same cluster.

Figure 19 – Execution time in ms of the L4R benchmark in isolation (blue) and contending with 3 instances of L4W (green).

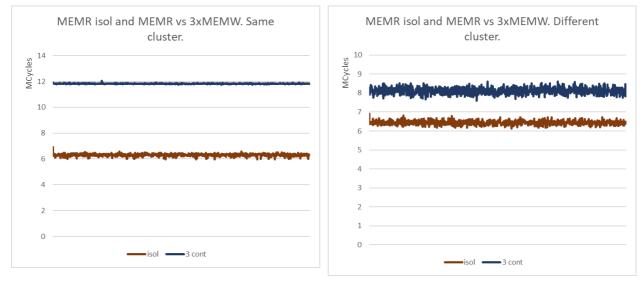

#### 3.2.6.4 MEM

In this experiment we run a MEMR benchmark against 3 instances of MEMW benchmarks. Each benchmark executes in one of the cores of a given cluster. Figure 20 below shows the execution time of the MEMR benchmark. As it can be seen in Figure 20a, the execution time is greatly affected by contenders running in the same cluster. Meanwhile, Figure 20b shows a smaller difference in execution time when contenders run in a different cluster.

(a) Execution time of MEMR in isolation and with contenders running on the same cluster.

(b) Execution time of MEMR in isolation and with contenders running on the different cluster.

Figure 20 – Execution time in ms of the MEMR benchmark in isolation (brown) and contending with 3 instances of MEMW (blue).

### 3.3 Technological assessment

In accordance with the task main objectives, we have been performing an in-depth analysis of the hardware platform to understand and identify the major sources of timing interference at the software and hardware level. At the software level, we have been focusing on the SAFEXPLAIN software stack and adapted our analysis, when possible, to address the contribution of the different software layer (operating system, ROS2 layer, and SAFEXPLAIN middleware). At the hardware level, we complemented the available documentation on the NVIDIA Orin with results from an ad-hoc test campaign, supporting hypothesis defined building on long-standing hardware and software expertise.

With the work done until month 18, we have already captured the main objectives of this task and produced a detailed analysis of the hardware platform, covering both functional and non-functional aspects. We have also identified the sources of timing interferences (interference channels) at both software and hardware level, which serves as an input to T4.3 and WP2.

#### Delivered tool and positioning in the SAFEXPLAIN stack

The result of this task is not a tool but consolidated knowledge on which further project-level decisions are taken. As such, it does not occupy concrete position in the SAFEXPLAIN stack.

#### **Intra-WP dependencies**

Within the scope of WP4, the obtained results are fundamental inputs to other tasks.

- T4.2: The identification of the main sources of hardware interference steers the selection of those events and monitors that are critically relevant for timing and interference analysis. It is also important that both tasks work consistently towards achieving WP4 objectives.

- T4.3: The sources of timing interference and the mitigation actions identified in T4.1 are in fact determining the strategy to follow for timing and interference analysis, where the particular solution for supporting isolation among application must be modelled.

#### Inter-WP contribution and alignment

The contributions of this task are also relevant in the scope of other work packages. The analysis results are supporting many of the deployment decisions that are taken when tailoring and bringing software and concepts to the actual target.

- WP2: The sources of hardware interference and segregation solutions are critical aspects to be considered in the definition of the FUSA architecture and in particular of the Safety Patterns, where a concrete mapping of applications/components to the platform is required. Task 2.4 is explicitly defined to favor the transition from FUSA concepts to corresponding deployment configurations.

- WP5: The hardware analysis results can be exploited by use case providers to take informed decisions on where and how to deploy the applications.

The alignment with other work packages, and WP2 in particular, is guaranteed by the continuous interaction between the work packages.

#### T4.1 Next steps

Task T4.1 is running until m24. The hardware and software analyses have already produced a deep understanding of the platform, providing a more than appropriate level of details to execute the other project tasks. We have no relevant component or major area of interest in the hardware left to be analysed. In the next project period, the task will be capturing any emerging requirements from other tasks and work-packages, with bearing on hardware and low-level software aspect. The task will also support WP2 for incremental deployment of Safety Patterns.

# 4 Observability Channels (T4.2)

Information on low-level hardware events is typically made available in modern Commercial Off The Shelves (COTS) platform via specialized hardware support provided by more or less complex Platform Monitoring Units (PMU). This task identifies and tests the platform monitors (hardware event monitors or HEMs) providing information about timing behavior, multicore timing interference, shared resource usage, and many more metrics. In the scope of WP4 observability is fundamental to run other tasks. Among all HEMs, we then make a selection of those needed to properly predict the timing behaviour of running applications, as needed by the statistical timing estimation techniques in T4.3. Another key activity of this task is producing a monitor configuration support library integrated in the software stack to collect as many measurements as needed for relevant monitors for timing prediction in T4.3. We refer to this library as *PMULib* (Performance Monitoring Unit Library).

In this section, we start with identifying the need for observability in SAFEXPLAIN. We then identify the set of HEMs that are available in the platform. We introduce PMULib, a fundamental tool in SAFEXPLAIN to make HEMs accessible to all other tasks on top of SAFEXPLAIN stack. We then make an analysis of the HEMs accuracy and single out those HEMs that better help tracking timing-related aspects, including multicore contention.

### 4.1 PMU and HEM analysis

Observability is a fundamental property embedded critical platform must fulfil in order to enable the collection of evidence on the behavior of the system at execution and exploit such information to perform various types of analysis. Different hardware platforms come with different observability support: depending on the debug support for the different hardware units, the degrees of observability may largely vary across products.

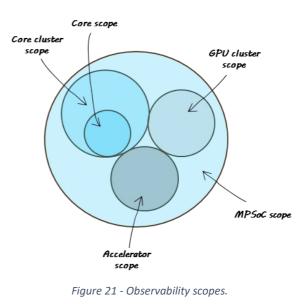

When considering the Orin platform, we were aware of the observability support granted by ARM Cortex CPUs, the main interconnect, as well as in the previous family of AGX platform (Jetson AGX). Due to the complexity and heterogeneity of the platform, we had first to understand the different

support available in each of the different scopes in the Orin: CPU cluster, GPU cluster, Accelerators, and MPSoC levels (see Figure 21).

### 4.1.1 Use of hardware-level information in SAFEXPLAIN

The set of events happening at the hardware level, and gathered through HEMs, has been increasingly considered as a valuable source of information to decipher the deepest details of hardware design and ultimately of software execution. SAFEXPLAIN fully recognizes the usefulness of hardware-level information and identified the need to collect this type of information and make it available to the tools and analyses designed and developed in the project.

We identified different aspects and activities in SAFEXPLAIN that justify the collection of hardware events:

- <u>Hardware analysis:</u> Collecting empirical evidence to support reverse engineering activity on the platform, which is often required to corroborate or clarify hardware features and operational details that are loosely documented in the officially available documentation. This cover, for example, the exact ID of hardware modules or the assessment of a partitioning mechanism. This objective is therefore instrumental to **T4.1** goals.

- <u>System monitoring</u>: Supporting on-line monitoring of low-level behaviour of target applications. The library allows to track relevant events, for example, to measure and limit the impact of multicore timing interference on a software partition. This objective is therefore instrumental to **T4.1** goals and ultimately to **WP2 (T2.4)** goals.

- <u>Timing characterization</u>: Supporting timing characterization by enabling the collection of timing information while the program executes and use it later to reason on the application timing behavior. Timing information, including execution time and other resource usage metrics, are fundamental information for measurement-based timing analysis approaches and SAFEXPLAIN is indeed focusing on statistical measurement-based methods for the analysis of complex AI-based systems. This objective is therefore instrumental to **T4.3** goals.

These aspects motivated the analysis of observability support on the target platform and, subsequently, the design and development of a user-level library to make hardware events easily accessible to SAFEXPLAIN tools and on top of the project hardware and software stack.

As the first step in the overall strategy followed to adequately exploit platform-level observability we analysed the actual support offered by the target hardware, which implies understanding the support on the many hardware modules and the complementary support offered by module-specific monitoring units and monitoring libraries. The support, in fact, depends on the manufacturer design but also on the specific model as support may largely vary even within the same family of products. This is the case, for example, of configuration and monitoring control in advanced accelerator. We assessed the offered support against the planned use in the scope of the project. We concluded that, although the support is not the same as that offered in high-end platform for mainstream (i.e. not embedded) market, all SAFEXPLAIN scopes are sufficiently covered by the available support.

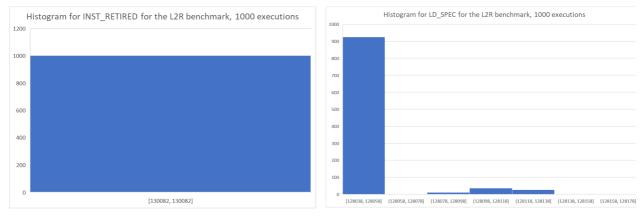

Moreover, we also had to ensure the sources of information was ultimately trustworthy, in terms of correctness and accuracy. This activity consisted in selecting test scenario with well-known behavior in terms of hardware events and assessing HEMs observed values against expected ones.

## 4.2 HEMs identification

There are two main hardware blocks that expose HEMs that can be used. The A78 [3] cores and the SCF [8].

- The HEMs of the A78 focus on cpu, DL1 caches, L2 and L3. They are architectural HEMs described in the architecture manual [3]. They can be accessed with very low latency.

- The HEMs of the System Coherency Fabric (SCF), an uncore component connecting the CPU Complex and the GPU Complex to the Memory Controller Fabric. These HEMs are poorly documented and take a very high latency to be accessed.

We analysed a total of 130 HEMs and developed a taxonomy organizing the best candidates in 8 classes:

- cpu-pipeline, counting events generated at core level by the pipeline

- bus-memory accesses, counting accesses to the main bus

- TLB, grouping different types of events involving DL1 (data cache), IL1 (instruction cache), and L2 TLBs (Transaction Lookaside Buffer)

- IL1, grouping different types of accesses to the instruction cache

- DL1, grouping different types of accesses to the data cache

- L2, grouping different types of accesses to private L2 cache

- L3, grouping different types of accesses to cluster-shared L3 cache

- SCF, grouping different types of accesses to shared SCF (including L4 cache events)

Using this taxonomy, we selected a series of HEMs as most promising. Their selection is based on their expected usefulness to predict the impact the software could have on the shared resources.

As it can be seen the HEMs in the subsections below are related to the number of accesses and misses to each cache level, the accesses to shared resources in the data path, and to program execution. Those HEMs are the ones that most closely could predict the amount of pressure put on the hardware shared resources by the program being executed.

### 4.2.1 CPU-pipeline HEMs

| Mnemonic     | Description                                                                                                                           | ID   |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|--|

| INST_RETIRED | ED Instruction architecturally executed. This event counts all retired instructions, including those that fail their condition check. |      |  |  |  |  |

| BR_PRED      | Predictable branch speculatively executed. This event counts all predictable branches.                                                | 0x12 |  |  |  |  |

| LD_SPEC      | Operation speculatively executed, load                                                                                                | 0x70 |  |  |  |  |

| ST_SPEC      | Operation speculatively executed, store                                                                                               | 0x71 |  |  |  |  |

### 4.2.2 Instruction cache HEMs (L1I)

| Mnemonic         | Description                                                                                                                                                                                                                                                                                            | ID     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| L1I_CACHE_REFILL | <ul> <li>L1 instruction cache refill. This event counts any instruction fetch which misses in the cache.</li> <li>The following instructions are not counted:</li> <li>Cache maintenance instructions</li> <li>Non-cacheable accesses</li> </ul>                                                       | 0x1    |

| L1I_CACHE        | <ul> <li>L1 instruction cache access or L0 Macro-op cache access. This event counts any instruction fetch which accesses the L1 instruction cache or L0 Macro-op cache. The following instructions are not counted:</li> <li>Cache maintenance instructions</li> <li>Non-cacheable accesses</li> </ul> | 0x14   |

| L1I_CACHE_LMISS  | L1 instruction cache long latency miss                                                                                                                                                                                                                                                                 | 0x4006 |

### 4.2.3 Data cache HEMs (L1D)

| Mnemonic         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ID  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| L1D_CACHE_REFILL | <ul> <li>L1 data cache refill. This event counts any load or store operation or page table walk access which causes data to be read from outside the L1, including accesses which do not allocate into L1.</li> <li>The following instructions are not counted:</li> <li>Cache maintenance instructions and prefetches</li> <li>Stores of an entire cache line, even if they make a coherency request outside the L1</li> <li>Partial cache line writes which do not allocate into the L1 cache</li> <li>Non-cacheable accesses.</li> </ul> | 0x3 |

|                                           | This event counts the sum of L1D_CACHE_REFILL_RD and L1D_CACHE_REFILL_WR.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| L1D_CACHE                                 | L1 data cache access. This event counts any load or store operation or page table<br>walk access which looks up in the L1 data cache. In particular, any access which could<br>count the L1D_CACHE_REFILL event causes this event to count.<br>The following instructions are not counted:<br>Cache maintenance instructions and prefetches<br>Non-cacheable accesses<br>This event counts the sum of L1D_CACHE_RD and<br>L1D_CACHE_WR.                                                                                     | 0x4  |

| L1D_CACHE_WB                              | L1 data cache Write-Back. This event counts any write-back of data from the L1 data<br>cache to L2 or L3. This counts both victim line evictions and snoops, including cache<br>maintenance operations.<br>The following instructions are not counted:<br>Invalidations which do not result in data being transferred out of the L1<br>Full-line writes which write to L2 without writing L1, such as write streaming<br>mode                                                                                               | 0x15 |

| L1D_CACHE_LMISS_RD                        | L1 data cache long-latency miss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0x39 |

| L1D_CACHE_RD                              | L1 data cache access, read. This event counts any load operation or page table walk<br>access which looks up in the L1 data cache. In particular, any access which could<br>count the<br>L1D_CACHE_REFILL_RD event causes this event to count.<br>The following instructions are not counted:<br>Cache maintenance instructions and prefetches<br>Non-cacheable accesses                                                                                                                                                    | 0x40 |

| L1D_CACHE_WR                              | L1 data cache access, write. This event counts any store operation which looks up in<br>the L1 data cache. In particular, any access which could count the<br>L1D_CACHE_REFILL_WR event causes this event to count.<br>The following instructions are not counted:<br>Cache maintenance instructions and prefetches<br>Non-cacheable accesses                                                                                                                                                                               | 0x41 |

| L1D_CACHE_REFILL_RD                       | L1 data cache refill, read. This event counts any load operation or page table walk<br>access which causes data to be read from outside the L1, including accesses which do<br>not allocate into L1.<br>The following instructions are not counted:<br>Cache maintenance instructions and prefetches<br>Non-cacheable accesses                                                                                                                                                                                              | 0x42 |

| L1D_CACHE_REFILL_WR                       | <ul> <li>L1 data cache refill, write. This event counts any store operation which causes data to be read from outside the L1, including accesses which do not allocate into L1.</li> <li>The following instructions are not counted: <ul> <li>Cache maintenance instructions and prefetches</li> <li>Stores of an entire cache line, even if they make a coherency request outside the L1</li> <li>Partial cache line writes which do not allocate into the L1 cache</li> <li>Non-cacheable accesses</li> </ul> </li> </ul> | 0x43 |

| L1D_CACHE_REFILL_INNER                    | L1 data cache refill, inner. This event counts any L1 data cache linefill (as counted by L1D_CACHE_REFILL) which hits in the L2 cache, L3 cache or another core in the cluster.                                                                                                                                                                                                                                                                                                                                             | 0x44 |

| L1D_CACHE_REFILL_OUTER                    | L1 data cache refill, outer. This event counts any L1 data cache linefill (as counted by L1D_CACHE_REFILL) which does not hit in the L2 cache, L3 cache or another core in the cluster, and instead obtains data from outside the cluster.                                                                                                                                                                                                                                                                                  | 0x45 |

|                                           | L1 data cache write-back, victim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0x46 |

| L1D_CACHE_WB_VICTIM                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

| L1D_CACHE_WB_VICTIM<br>L1D_CACHE_WB_CLEAN | L1 data cache write-back cleaning and coherency                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0x47 |

### 4.2.4 L2 cache HEMs (L2)

| Mnemonic  | Description                                                                                                                                                                                                                       | ID   |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| L2D_CACHE | L2 unified cache access. This event counts any transaction from<br>L1 which looks up in the L2 cache, and any write-back from the L1 to the L2. Snoops<br>from outside the core and cache maintenance operations are not counted. | 0x16 |

| L2D_CACHE_REFILL                                      | L2 unified cache refill. This event counts any Cacheable transaction from L1 which causes data to be read from outside the core. L2 refills caused by stashes and prefetches that target this level of cache, should not be counted.                                                                                                             |        |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| L2D_CACHE_WB                                          | L2 unified cache write-back. This event counts any write-back of data from the L2 cache to outside the core. This includes snoops to the L2 which return data, regardless of whether they cause an invalidation. Invalidations from the L2 which do not write data outside of the core and snoops which return data from the L1 are not counted. |        |

| L2CACHE_INV                                           | L2 unified cache invalidate                                                                                                                                                                                                                                                                                                                      | 0x58   |

| L2D_CACHE_LMISS_RD L2 unified cache long latency miss |                                                                                                                                                                                                                                                                                                                                                  | 0x4009 |

### 4.2.5 L3 cache HEMs (L3)

| Mnemonic                                                                                                                                                                                                                                                                                                                                                                                                                            | nemonic Description                                                                                                                                                                                                                                 |        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| L3D_CACHE_ALLOCATE                                                                                                                                                                                                                                                                                                                                                                                                                  | Attributable L3 unified cache allocation without refill. This event counts any full cache line write into the L3 cache which does not cause a linefill, including write-<br>backs from L2 to L3 and full-line writes which do not allocate into L2. |        |

| L3D_CACHE_REFILL<br>L3D_CACHE_REFILL<br>Attributable L3 unified cache refill.<br>This event counts for any cacheable read transaction returning data from the SCU for<br>which the data source was outside the cluster. Transactions such as ReadUnique are<br>counted here as 'read' transactions, even though they can be generated by store<br>instructions.<br>Prefetches and stashes that target the L3 cache are not counted. |                                                                                                                                                                                                                                                     | 0x2a   |

| L3D_CACHE         Attributable L3 unified cache access.           This event counts for any cacheable read transaction returning data from the SCU for any cacheable write to the SCU.                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                     | 0x2b   |

| L3_CACHE_RD                                                                                                                                                                                                                                                                                                                                                                                                                         | L3 cache read                                                                                                                                                                                                                                       | 0xa0   |

| L3D_CACHE_LMISS_RD                                                                                                                                                                                                                                                                                                                                                                                                                  | L3 unified cache long latency miss                                                                                                                                                                                                                  | 0x400b |

### 4.2.6 Bus-memory HEMs

| Mnemonic         | Bus access. This event counts for every beat of data transferred over the data channels between the core and the SCU. If both read and write data beats are                                                                                                                                                                                                              |      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| BUS_ACCESS       |                                                                                                                                                                                                                                                                                                                                                                          |      |

| BUS_ACCESS_RETRY | Bus access write. This event counts for every beat of data transferred over the write data channel between the core and the SCU.                                                                                                                                                                                                                                         |      |

| MEM_ACCESS       | <ul> <li>Data memory access. This event counts memory accesses due to load or store instructions.</li> <li>The following instructions are not counted: <ul> <li>Instruction fetches</li> <li>Cache maintenance instructions</li> <li>Translation table walks or prefetches</li> </ul> </li> <li>This event counts the sum of MEM_ACCESS_RD and MEM_ACCESS_WR.</li> </ul> |      |

| MEM_ACCESS_RD    | Data memory access, read. This event counts memory accesses due to load<br>instructions. The following instructions are not counted:<br>• Instruction fetches<br>• Cache maintenance instructions<br>• Translation table walks<br>• Prefetches                                                                                                                           |      |

| MEM_ACCESS_WR    | <ul> <li>Data memory access, write. This event counts memory accesses due to store instructions.</li> <li>The following instructions are not counted: <ul> <li>Instruction fetches</li> <li>Cache maintenance instructions</li> <li>Translation table walks</li> <li>Prefetches</li> </ul> </li> </ul>                                                                   | 0x67 |

| REMOTE_ACCESS    | Access to another socket in a multi-socket system                                                                                                                                                                                                                                                                                                                        | 0x31 |

### 4.2.7 TLB HEMs

| Mnemonic                                                                                                                                                      | Description                                                                                                                                                                                                                                                                                                                                      | ID   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| L1I_TLB_REFILL                                                                                                                                                | <ul> <li>L1 instruction TLB refill. This event counts any refill of the instruction L1 TLB from the L2 TLB. This includes refills that result in a translation fault.</li> <li>The following instructions are not counted:</li> <li>TLB maintenance instructions</li> <li>This event counts regardless of whether the MMU is enabled.</li> </ul> |      |

| L1D_TLB                                                                                                                                                       | L1 data TLB access. This event counts any load or store operation which accesses<br>the data L1 TLB. If both a load and a store are executed on a cycle, this event counts<br>twice. This event counts regardless of whether the MMU is enabled.                                                                                                 | 0x25 |

| L1 instruction TLB access. This event counts any instruction fetch which acces instruction L1 TLB. This event counts regardless of whether the MMU is enabled |                                                                                                                                                                                                                                                                                                                                                  | 0x26 |

| L2TLB_REFILL                                                                                                                                                  | Attributable L2 unified TLB refill. This event counts on any refill of the L2 TLB, caused by either an instruction or data access. This event does not count if the MMU is disabled.                                                                                                                                                             |      |

| L2TLB_REQ                                                                                                                                                     | Attributable L2 unified TLB access. This event counts on any access to the L2 TLB (caused by a refill of any of the L1 TLBs).<br>This event does not count if the MMU is disabled.                                                                                                                                                               | 0x2f |

| L2TLB_RD_REFILL                                                                                                                                               | L2 unified TLB refill, read                                                                                                                                                                                                                                                                                                                      | 0x5c |

| L2TLB_WR_REFILL                                                                                                                                               | L2 unified TLB refill, write                                                                                                                                                                                                                                                                                                                     | 0x5d |

| L2TLB_RD_REQ                                                                                                                                                  | L2 unified TLB access, read                                                                                                                                                                                                                                                                                                                      | 0x5e |

| L2TLB_WR_REQ                                                                                                                                                  | L2 unified TLB access, write                                                                                                                                                                                                                                                                                                                     | 0x5f |

### 4.2.8 SCF HEMs

| Mnemonic                        | Description                                | ID      |

|---------------------------------|--------------------------------------------|---------|

| SCF_BUS_ACCESS                  | Bus accesses in the SCF                    | 0x10190 |

| SCF_BUS_ACCESS_RD               | BUS_ACCESS_RD Read bus accesses in the SCF |         |

| SCF_BUS_ACCESS_WR               | Write bus accesses in the SCF              | 0x10610 |

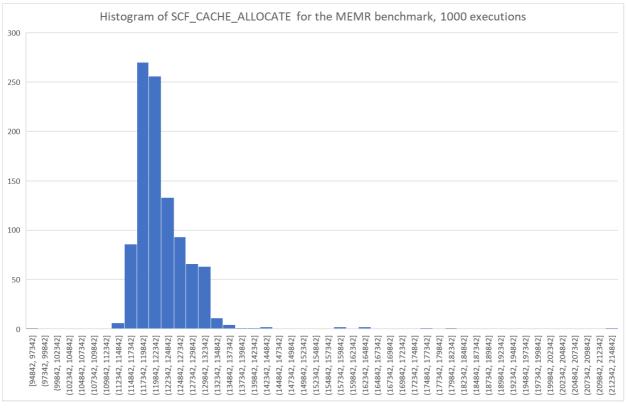

| SCF_CACHE_ALLOCATE              | SCF L4 cache allocates                     | 0x10f00 |

| SCF_CACHE_REFILL                | SCF_CACHE_REFILL SCF L4 cache refills      |         |

| SCF_CACHE SCF L4 cache accesses |                                            | 0x10f20 |

| SCF_CACHE_WB                    | SCF L4 cache write-backs                   | 0x10f30 |

### 4.3 Hardware Event Monitors PMULib

Once we identified the HEMs that could be used to track contention, our next step relates to developing a library to read it.

### 4.3.1 PMULib

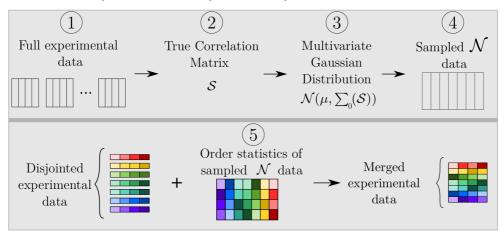

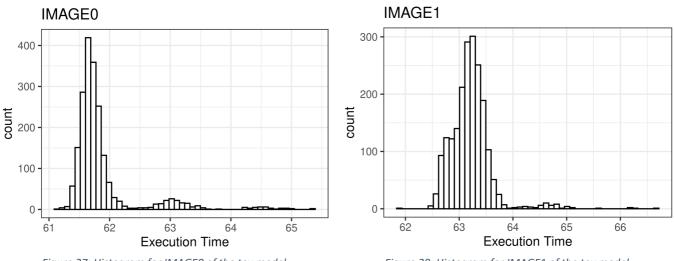

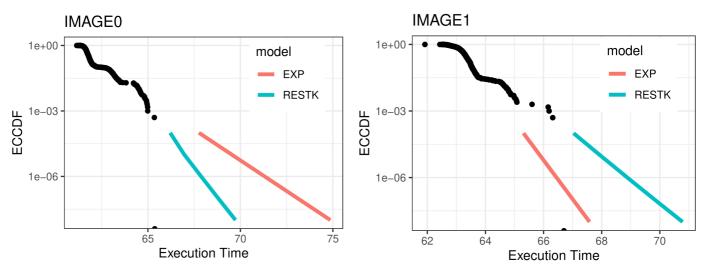

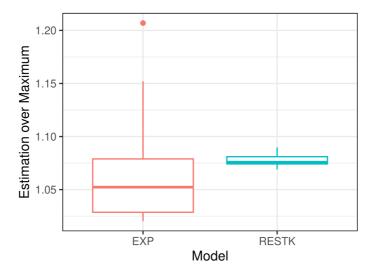

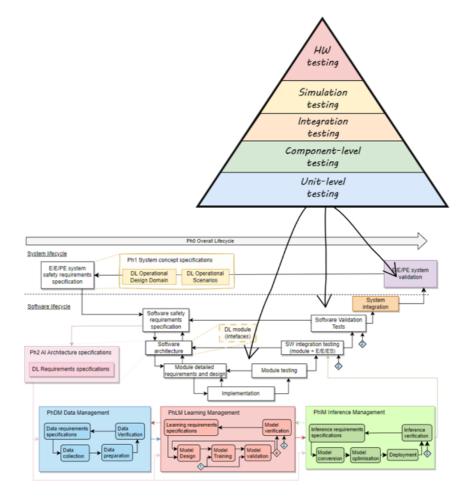

During this first period, BSC worked on the design and implementation of <u>PMULib</u> a platform specific lightweight library to configure and extract (collect) values from the different event monitors in the Orin platform, exploiting the available support at the different scopes. PMULib is a fundamental tool for supporting the required degree of platform observability necessary to support diverse elements in the SAFEXPLAIN technological stack (see Figure 22):