Safe and Explainable

Critical Embedded Systems based on AI

## D2.3 Safety Concept

Version 1.0

### Documentation Information

|                      |                                                                                                |

|----------------------|------------------------------------------------------------------------------------------------|

| Contract Number      | 101069595                                                                                      |

| Project Website      | <a href="http://www.safexplain.eu">www.safexplain.eu</a>                                       |

| Contractual Deadline | 31.03.2025                                                                                     |

| Dissemination Level  | PU                                                                                             |

| Nature               | R                                                                                              |

| Authors              | Javier Fernández (IKR), Giuseppe Nicosia (EXI), Francesca Guerrini (EXI), Stefano Lodico (EXI) |

| Contributors         | Irune Yarza (IKR), Irune Agirre (IKR), Carlo Donzella (EXI)                                    |

| Reviewed by          | Enrico Mezzetti (BSC)                                                                          |

| Keywords             | AI, Functional Safety, V&V, Catalog Scenarios, Safety Concept                                  |

This project has received funding from the European Union's Horizon Europe programme under grant agreement number 101069595.

## Change Log

| Version | Description Change                                         |

|---------|------------------------------------------------------------|

| V0.1    | First draft                                                |

| V0.2    | Second draft after addressing internal reviewer's comments |

| V1.0    | First consolidated version                                 |

|         |                                                            |

# Table of Contents

|                                                                      |    |

|----------------------------------------------------------------------|----|

| 1. Introduction .....                                                | 5  |

| 2. Safety Concept .....                                              | 6  |

| 2.1. Safe technical assessment and expert certification review ..... | 6  |

| 3. DL Safety Lifecycle for DL-software V&V .....                     | 8  |

| 3.1. Scenario catalogue and related test matrix .....                | 9  |

| 3.2. Focus STPA (triggering condition) and related test matrix ..... | 11 |

| 3.3. Example of V&V strategy application .....                       | 12 |

| 3.3.1. Automotive Use Case .....                                     | 13 |

| 3.3.2. Railway Use Case .....                                        | 19 |

| 3.3.3. Aerospace Use Case .....                                      | 26 |

| 4. Acronyms and Abbreviations .....                                  | 31 |

| 5. Bibliography .....                                                | 32 |

| 6. Annexes .....                                                     | 33 |

| Annex A: Railway Safety Concept .....                                | 33 |

| Annex B: Review meeting presentation .....                           | 33 |

## Executive Summary

This document includes an update of D2.1 and D2.2, incorporating enhancements and additions to the previously established Deep Learning (DL) software Verification and Validation (V&V) strategy ([deliverable D2.1](#)) and the development of a safety concept for a railway case study.

This safety concept aims to assess the previously defined strategies and specific solutions for implementing safety patterns in safety-critical software systems that incorporate Artificial Intelligence (AI) components (previously included in [deliverable D2.2](#)). The architectural solutions proposed in the railway case study seek to identify potential inconsistencies in the approach, address any contradictions with the requirements of the Bases of Assessment, and evaluate the feasibility of applying the approach within the given context.

# 1. Introduction

This document compiles the results from all tasks developed in Work Package (WP) 2: T2.1, T2.2, T2.3, T2.4, and T2.5. The objective of these tasks is to define and evaluate functionalities based on DL components that are safety-related or whose use may have implications for safety functions.

Specifically, this deliverable establishes a safety concept for the railway use case, following the lifecycle developed in the SAFEXPLAIN project (T2.1, [deliverable D2.1](#)) and including relevant safety architectural design patterns for different DL usage levels (T2.3, [deliverable D2.2](#)). This safety concept serves as a foundation for validation by a certification authority, supporting future industrialization. Additionally, this deliverable expands the previously defined V&V strategy (task T2.2, [deliverable D2.1](#)). The results will be used to validate the railway case study approach, which is a key task within WP2. Instead of partially sharing the content of T2.4, we reserve part of it for deliverable D2.5, where the final progress on this task will be presented.

Since this deliverable updates and completes the content previously introduced in [deliverable D2.1](#) and [deliverable D2.2](#), we aimed to minimize redundancy across deliverables by avoiding repeating information whenever possible. Therefore, we refer the reader to those deliverables for background concepts and foundational aspects in case of any doubts.

This document is organized as follows:

- Section 0 introduces the railway case study and outlines the activities undertaken to analyze the feasibility of applying the proposed strategies and specific solutions for implementing safety patterns tailored to the railway domain. These efforts aim to assess their alignment with safety certification requirements through the development of a safety concept. Finally, this section presents the methodology followed for the safety assessment and the results obtained.

- Section 3 extend the V&V strategy previously introduced in deliverable D2.1 at vehicle and element level. To that end, at vehicle level this section defines a set of example scenarios related to the three use cases employed in SAFEXPLAIN project: railway (led by IKERLAN), automotive (led by EXIDA) and aerospace (Led by AIKO). Additionally, at element level this section analyses the triggering conditions derived through System-Theoretic Process Analysis (STPA), still for the three use cases. Finally, it includes examples of V&V strategy application in the three use cases defined in SAFEXPLAIN project.

## 2. Safety Concept

The main result of this document is the definition of the Safety Concept for railway case-study based on the SAFEXPLAIN contribution, and the documentation of the feedback provided by the certification authority.

The definition of the Safety Concept will serve to illustrate a practical application of the lifecycle procedure developed around the use of AI in safety domains. As outputs of the work regarding SAFEXPLAIN:

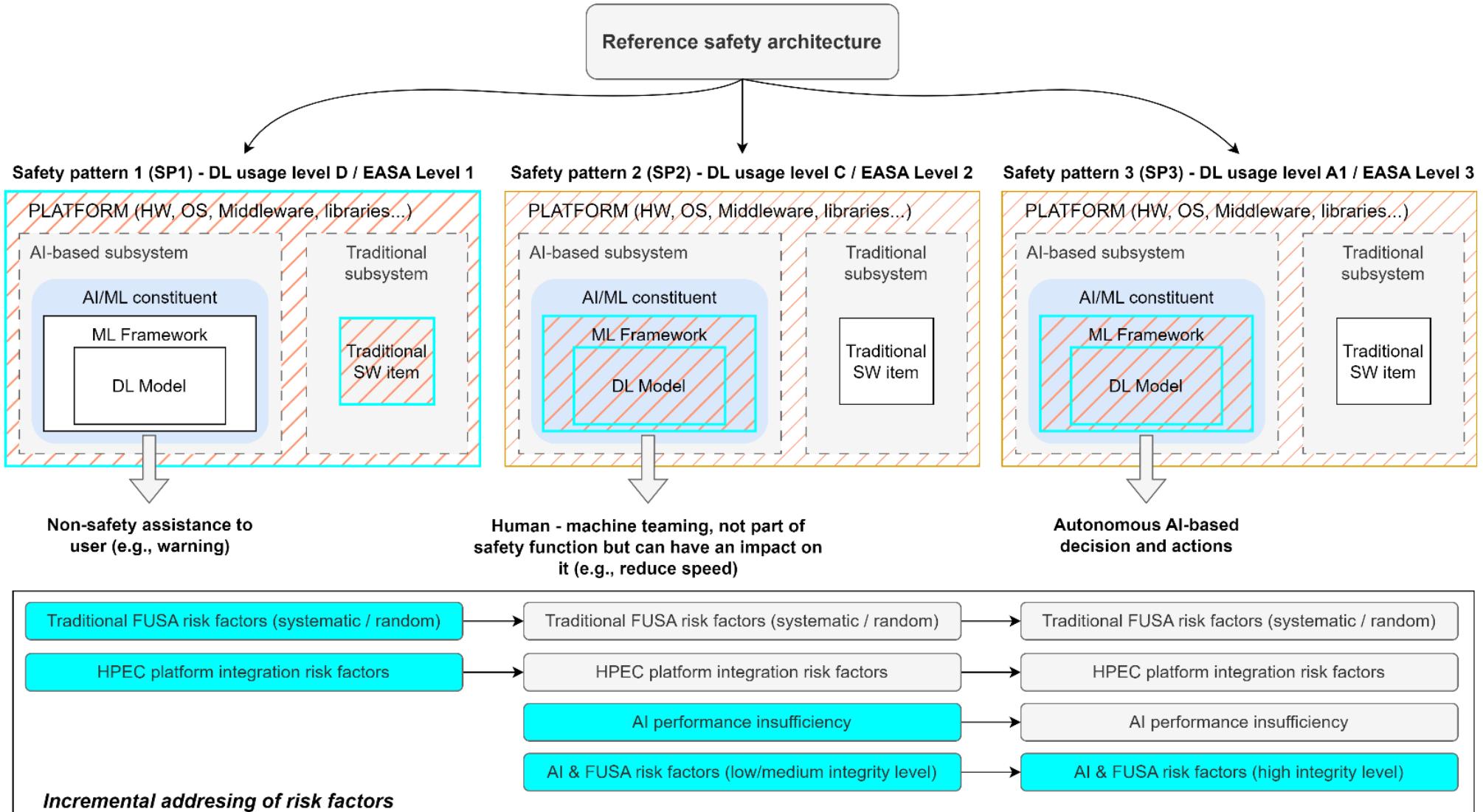

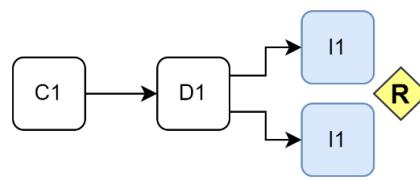

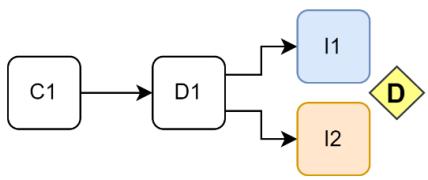

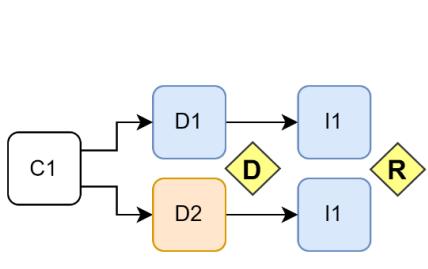

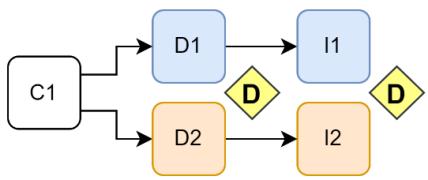

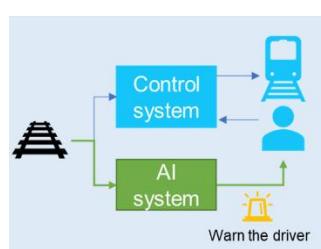

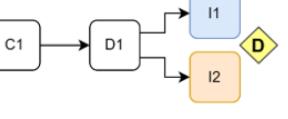

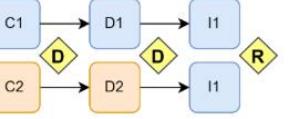

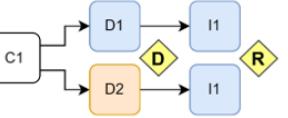

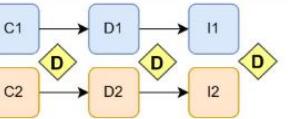

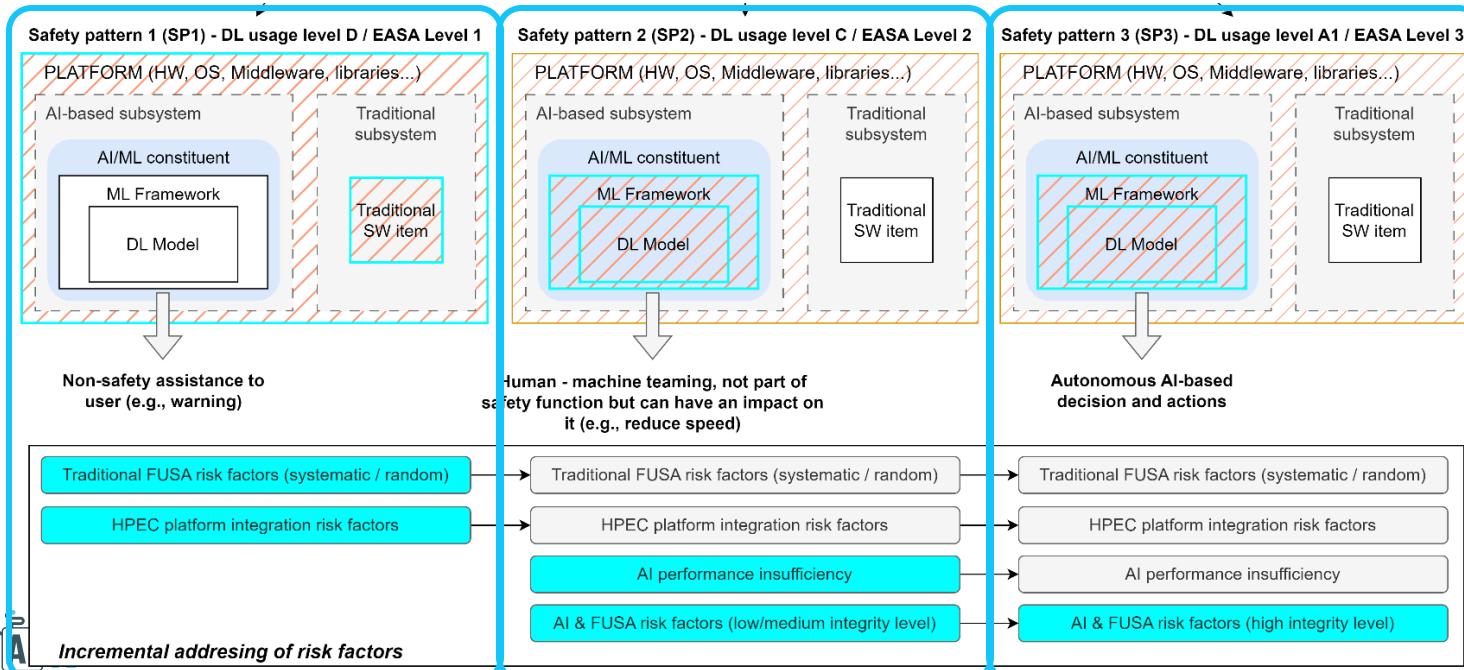

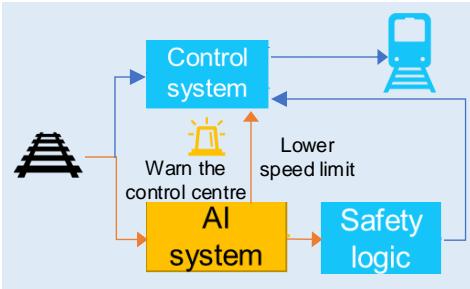

- The Railway Safety Concept is included in Annex A and is structured into three parts. The first part provides an informative introduction outlining the SAFEXPLAIN project and its main topics. The second part describes the reference safety architecture and safety patterns submitted for review by TÜV Rheinland, adapted and extended from deliverable D2.2. Finally, the third part defines the system concept specification of a railway domain object detector controller. This section follows an incremental strategy, progressing from the lowest DL usage level (Usage Level D / EASA Level 1) to the highest one (DL Usage Level A1 / EASA Level 3). It presents a set of safety patterns, proposing specific system architectures, safety techniques, and their application on the project's target platform (NVIDIA Orin).

- The presentation and the main open issues and comments discussed during the review meeting with TÜV Rheinland certification authority is provided in the Annex B. Additionally, the methodology followed in the assessment, as well as a summary of the main points discussed during the meeting, are reported.

### 2.1. Safe technical assessment and expert certification review

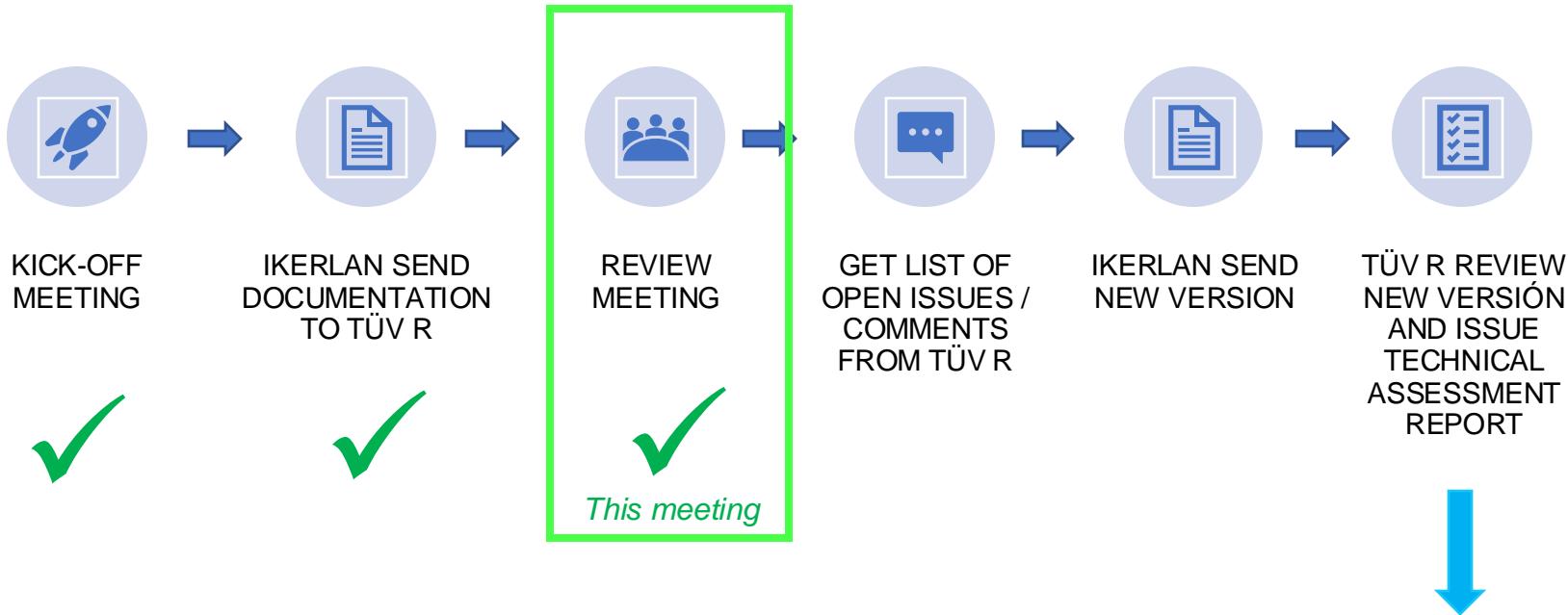

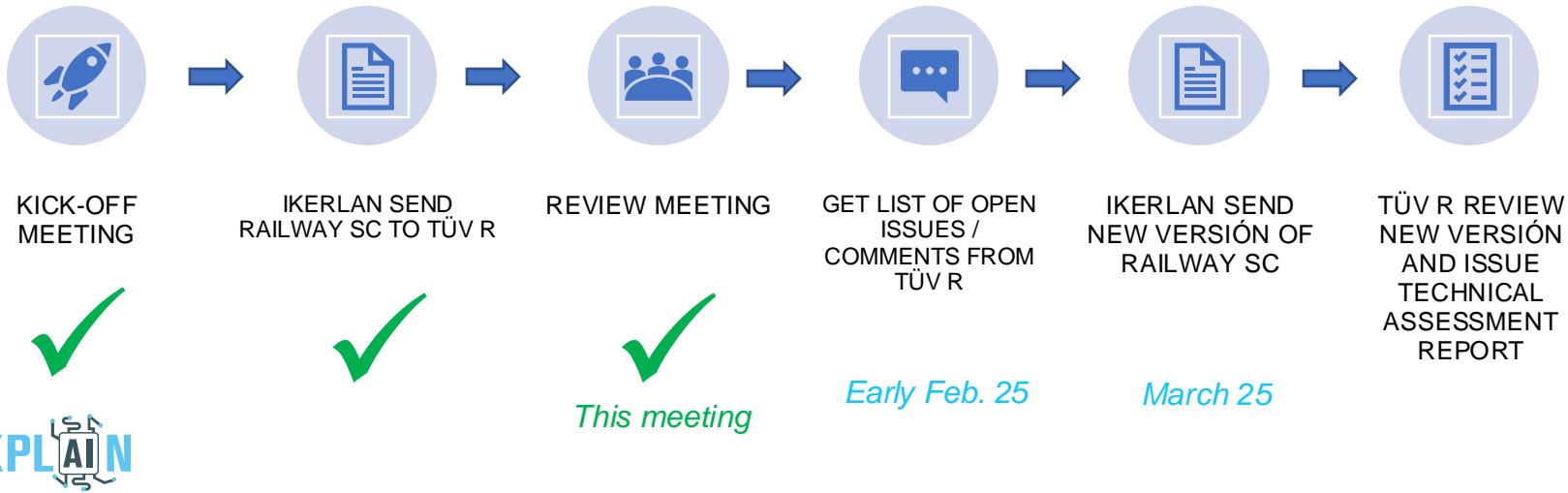

This subsection is related to Task T2.5, which is scheduled to run from month 13 to month 36. This task consists of two key activities: one focused on the AI-FSM and the other on the railway safety concept definition. The former was covered in deliverable 2.1, while the latter is addressed in this subsection. We have maintained the same methodology as explained in the deliverable D2.1, which is summarized in the Figure 1.

Figure 1. Safety concept review steps

We have included in the “Annex A: Railway Safety Concept” the same documentation sent to TÜV Rheinland and in the “Annex B: Review meeting presentation” we have included the review meeting presentation in which we discussed the main open issues and comments received from the first TÜV Rheinland assessment. The review meeting focused on information exchange and experience sharing related to these topics. At the time of writing of this deliverable, the TÜV Rheinland assessment have not been received yet. However, we can share the general impression, and the main points discussed during the review meeting and, once the final assessment is received, we will include its conclusions in deliverable D2.5.

One of the points discussed was related to AI risk factors and the complexity of identifying certain systematic faults during the design and V&V processes. In fact, we agreed that, due to the extremely high number of parameter variations in an AI model, these faults may not be easily detectable. However, they should not be considered random, but rather as systematic errors arising from those pseudorandom distributions that are difficult to detect.

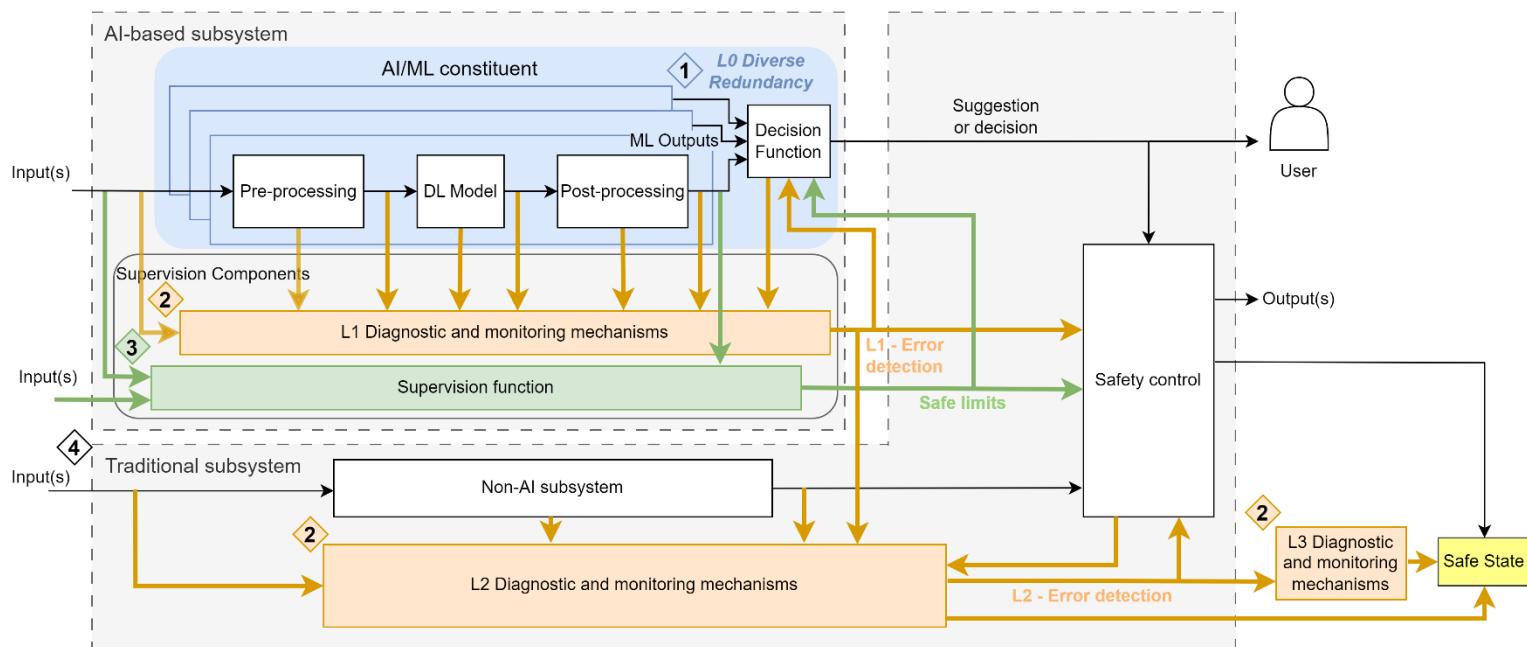

We discussed the importance of the decision function, which brings together the redundant channels and therefore it shall have more stringent requirement than those posed over the AI based SW components it gets the input from. They requested to be more specific about the explainability techniques that can be implemented in the supervision vision.

We discussed how the properties we identified for AI technology align with the clauses of ISO/IEC TR 5469. In this context, they proposed including clause 8.4.3, "Issues Related to Learning from the Environment," and explicitly mentioning the other relevant clauses.

From the system description, TÜV Rheinland expressed concerns about relying solely on cameras instead of incorporating diverse sensor technologies such as LIDAR or infrared cameras. We explained that this railway safety concept initially focuses on camera-based AI; however, our approach can be extended to include additional input technologies in future development phases.

Finally, as general impression, they conclude that we have provided a reasonable approach for an architectural solution tailored to a railway case study. In the same way, they conclude that our work outlines key strategies and tailored solutions for implementing safety patterns in safety-critical software systems that incorporate AI components.

Additionally, since from some AI-based parts the maximum Safety Integrity Level (SIL) is 3 or 4, they remarked that all hardware and software for this AI components shall fulfil the requirements imposed by traditional functional safety standards for the corresponding SIL. With a small joke, they were confident that IKERLAN would take it into account, given that we had considered the EASA documentation, where a system consists of a traditional system based on functional safety and another containing the AI component.

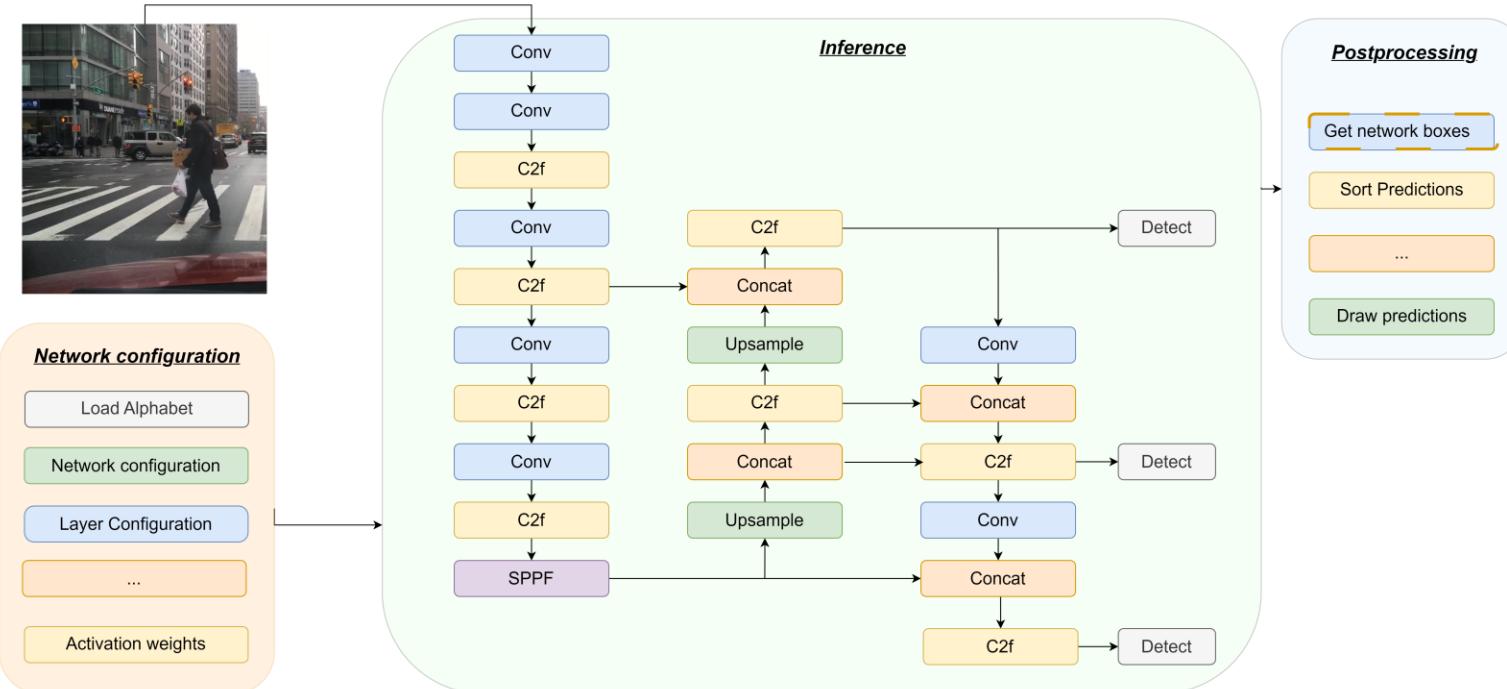

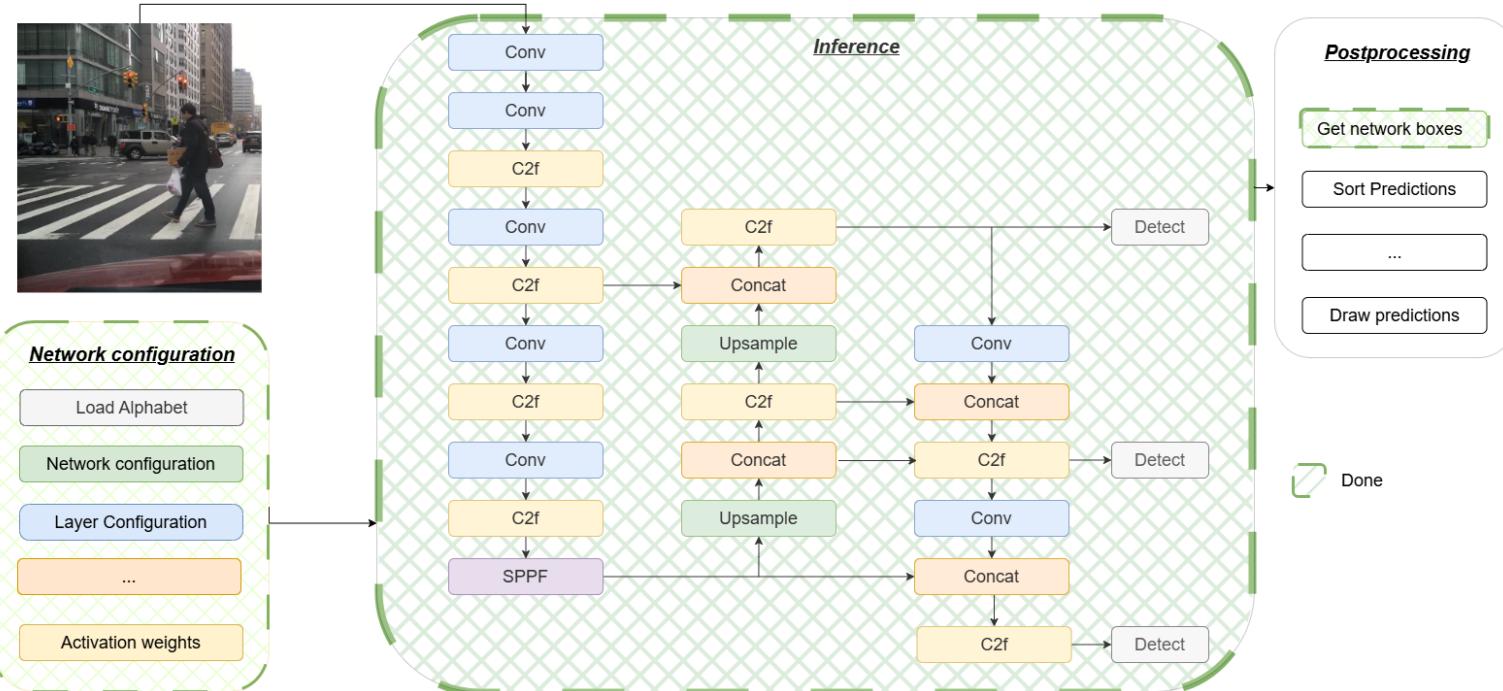

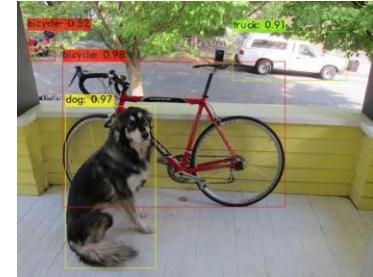

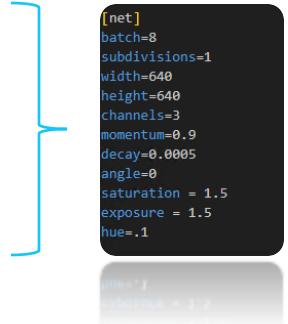

Additionally, we presented *safeYOLO*, a statically allocated memory adaptation of YOLOv4<sup>1</sup>. This implementation focuses on adapting the inference phase of YOLOv4 to comply with MISRA C, a widely used coding guideline. We discussed that this serves as a strong starting point for aligning the software implementation of AI-based systems with traditional functional safety standards. However, TÜV emphasized the need to also address insufficiencies related to the model itself, particularly those stemming from the training phase.

---

<sup>1</sup> <https://github.com/AlexeyAB/darknet>

### 3. DL Safety Lifecycle for DL-software V&V

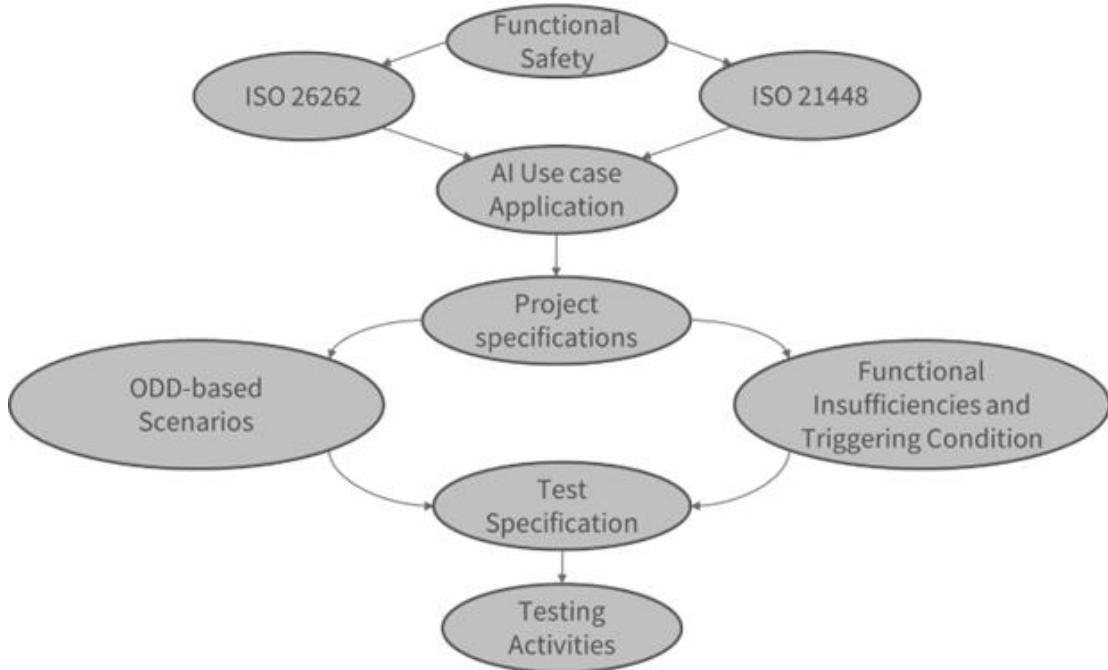

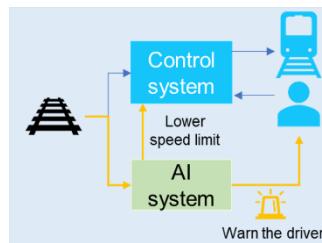

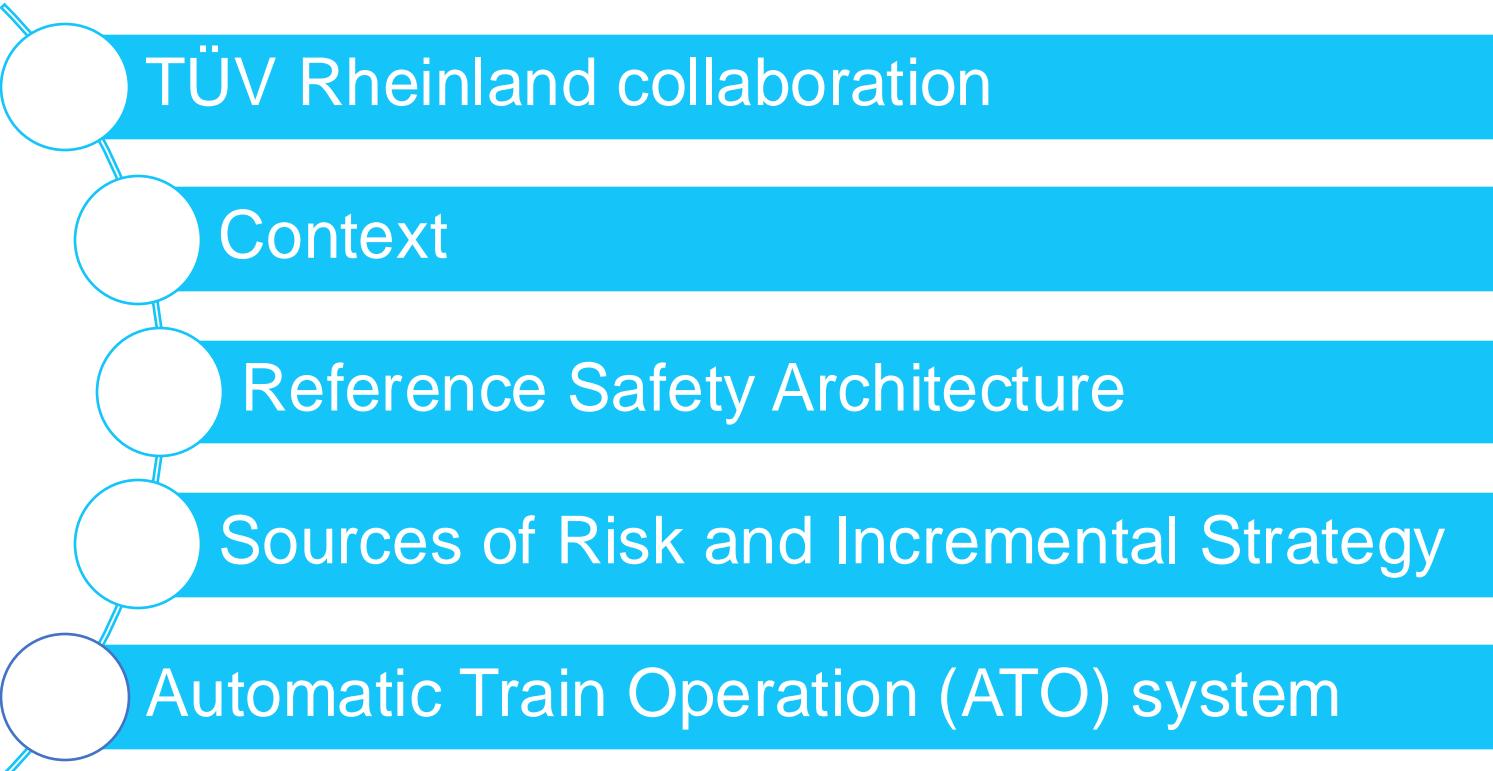

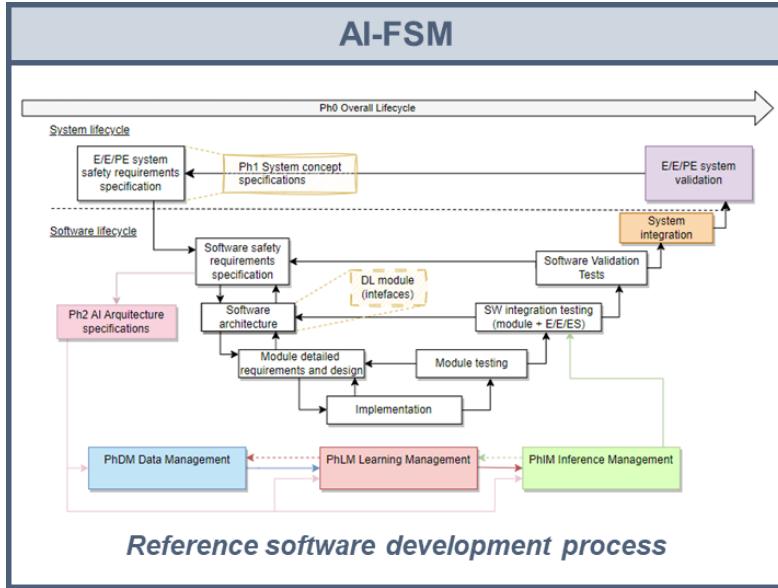

Figure 2, depicts the V&V strategy followed for each of the three use cases in the automotive, railway and aerospace domains deployed within the SAFEXPLAIN project.

Figure 2. V&V Strategy.

The adopted V&V strategy and the associated methods for the ML/DL-V&V extends the traditional FuSa approach by addressing also “*hazards resulting from functional insufficiencies*” as it was explained in the [deliverable D2.1](#). Our V&V strategy incorporates testing techniques based on those provided in ISO 26262 [1] standard and ISO 21448:2022[2], aiming to establish a valid method for verifying the intended functionalities at vehicle level (scenario-based) and at component level (triggering condition-based).

Since this deliverable is an extension of [deliverable D2.1](#), and to facilitate the reader's understanding, we have included relevant content from that document regarding the test methods used in the V&V strategy related to both ISO 26262 and ISO 21448:

- ISO 21448 (testing activities are focused on the scenarios):

- Analysis of environmental conditions and operational use cases (ISO 26262-4 Table 3 method 1h; ISO 21448 Table 6 Method H)

- Analysis of triggering conditions (Method N, Table 6)

- ISO 26262 (testing activities are focused on proving the safety requirements implementation and performance of safety mechanism):

- Requirements-based test (Method 1a - ISO 26262-4 table 13) Fault injection test (Method 1b - ISO 26262-4 table 13; Method 1d - ISO 26262-4 table 14)

- Fault injection test for triggering condition-based testing (ISO 26262-4 Table 4 method 1b; ISO 21448 Table 6 Method N)

- Long-term test (Method 1c - ISO 26262-4 table 13; Method 1b - ISO 26262-4 table 14; Method 1d - ISO 26262-4 table 16)

- Performance test (Method 1a - ISO 26262-4 table 14)

The main goal of the Verification & Validation (V&V) strategy is to:

- Find the hazardous scenarios related to the design

- Provide the evidence (e.g., test reports, ...) to prove the following:

- the Sense-Plan-Act elements (sensors and processing/decision algorithm) provide their proper functionality correctly

- the robustness of the system or functionality against the triggering condition

- the absence of unreasonable risk due to hazardous behaviour of the intended functionality

- the achievement of an acceptable risk level.

V&V strategy is applied both at vehicle level and component level:

- At vehicle level, a list of scenarios (Scenario Catalogue) has been defined which describes the intended functionality in real-life situations for each use case domain. From the catalogue of the scenarios the related test cases were derived to demonstrate, by following the steps defined in the test cases, that the intended functionality is behaving as specified and the residual risk meets the acceptance criteria (criteria which represent the absence of an unreasonable level of risk).

- A test matrix is derived from test specifications which will be executed, guided by the test matrix, to validate and ensure that the functionality works as expected. This test matrix will delineate the constraints and every value that should be set for each test step (e.g. ego vehicle, target vehicle, environment...). The test matrix also facilitates the documentation of the outcomes of each test conducted, to generate a descriptive report at the conclusion of the test activity.

- At element level, we have analysed the design through System-Theoretic Process Analysis (STPA) to:

- Identify the most critical triggering condition related to the elements design.

- Identify the missing safety mechanism (if any) to cover the triggering condition and bring the harm to an acceptable level implementing the needed functional modifications, or

- Define the test cases to test the safety mechanisms already implemented.

By following the steps defined in the test cases, the effectiveness of the implemented safety mechanisms is proved in identifying the system's weaknesses. Additionally, it is demonstrated that the intended functionality behaves as specified.

### 3.1. Scenario catalogue and related test matrix

The purpose of the scenario catalogue is to define the set of scenarios to describe how the intended functionality works when a specific relevant situation occurs. The scenario catalogue has been defined for each of the SAFEXPLAIN project use case domains: Automotive, Railway and Aerospace.

In every scenario, to enable the simulation for the testing activities, the following relevant conditions and constraints are specified:

- Conditions and/or constraints related to the ego vehicle (e.g., ego vehicle speed, ego vehicle acceleration, offset w.r.t. the target, initial distance from the target, ego vehicle status...).

- Conditions and/or constraints related to the vehicle identified as target (e.g., target vehicle speed, target vehicle acceleration, vehicle status...).

- Conditions/Constraints related to environment (e.g., luminosity, temperature...)

- Vehicles and Scenarios Pre-conditions (e.g., ego vehicles speed, ego vehicles path, override conditions, ....).

Depending on the use case different conditions and/or constraints have been reported, for example:

- For automotive:

- Steering, as well as yaw rate, could have a critical impact if not regulated, given their relevant exposure; therefore, thresholds were specified. Since steering and yaw are not applicable in railway and aerospace domains, thresholds for these domains were not specified.

- Road surface condition could have critical impact (unlike railway/aerospace), therefore the road surface condition is needed to be defined as the most common street in a good condition (asphalt and concrete).

- For Railway:

- Speed limit, when the train goes in/out the train station and when goes outside the train stations.

- Environmental condition:

- Unlike the automotive use case, this domain considers not only sunny days but also cloudy and rainy days, in accordance with the safety concept.

- In the automotive, scenarios in the night were also considered, but here the scenarios created are just in the daytime, since the night was excluded in the safety concept of the use case.

- For Aerospace:

- Since in the space no object can be stationary, we consider the target as reference frame, and we defined just the relative speed of the ego vehicle w.r.t. the target vehicle

- In the environmental conditions, since we are not in the earth:

- There is a different gravity acceleration which was assumed.

- The orbits where the ego vehicle flies are also specified (LEO/GEO).

- Since concepts of “day and night” is not applicable in the space, luminosity is defined not as a range of “intensity of pixels in the image”.

- Since we are in space, weather conditions are not applicable, so excluded.

Each scenario created is based on our everyday life experiences (if applicable) and the Operational Design Domain (ODD) where the constraints/conditions (by design) related to the functionality are defined.

The criteria to choose a scenario, is based on what the related test and analyses could reveal or confirm, as well the frequency with which the specific scenario could occur. A scenario that is rare is not worth analysing.

Indeed, only for the automotive domain, to quantify the probability of occurrence of a scenario (e.g., every 800 h...), we based on the VDA-702[1, 3], published by the German Association of the Automotive Industry, which describes every specific relevant situation and their exposure parameters (based on frequency and duration). Basically, it gives some “marks” to each situation and basing on these marks and the constraints derived from it (defined in the document itself) we defined the probability of occurrence.

In order to verify whether the intended functionality works as expected, every defined scenario must be validated through related testing activities which is regulated by related test case

specification which describes the test activity to be performed step by step, with constraints/conditions related to the specific step described.

These tests are necessary to analyse the functionality behaviour in that specific scenario and in those specific conditions. At the end of each testing activity, the outputs shall be evaluated to determine whether the acceptance criteria are met.

In order to manage and facilitate every testing activity, a test matrix derived from the test cases specification has been defined.

As it was previously outlined, the test matrix is a useful tool that maps every test case and let the tester to be guided in the testing activities. Its purpose focuses on:

- Indicate visually and in an easily comprehensible manner the constraints and conditions of the ego vehicle, as well as those of the environment, target vehicle and every value to be set in every test case.

- Describe how many repetitions of the tests shall be performed.

- Collect and assess the test result ensure a comprehensive report of the testing activity.

### 3.2. Focus STPA (triggering condition) and related test matrix

In order to identify potential specification insufficiencies, potential performance insufficiencies and potential triggering conditions leading to a hazardous behaviour a SOTIF analysis has been conducted by using STPA method.

STPA is an analysis of the hazards that could occur in a system, starting from the assumption that hazardous behaviour can also be caused even when no component may have failed. STPA is very useful to optimize the hazard/risk analysis techniques to guarantee that the intended functionality, also if the system is very complex, works correctly.

STPA analysis is developed in 4 steps:

1. Defining the purpose and scope of the analysis: Here is necessary to identify the losses to be prevented by analysing the design, which are vehicle-level states or conditions, with particular other conditions, will lead to a loss (harm). From the design safety critical hazard must be also derived and condition/constraints as well.

2. Modelling of the control structure: Here all the specifications are analysed to identify a list of control actions (CAs) of the system, which are how the intended functionality is expected to control that hazardous event.

3. Identification of unsafe control actions: Here we identify the Unsafe Control Actions (UCAs), which are actions (associated to the Hazard Analysis and Risk Assessment (HARA)) that, in a particular context and worst-case environment, will lead to a vehicle-level hazard. To ensure the UCAs are prevented, controller safety constraints (SCs) can be defined, specifying assertions on the controller behaviours that need to be satisfied to prevent UCAs from occurring.

4. Identification of causal scenarios: the final core step of STPA identifies the functional insufficiencies and triggering condition. The former refers to the limitation of the functionality caused by the triggering condition, while triggering conditions are the factors that initiate a subsequent system reaction leading to hazards. A triggering condition can be anything that causes a limitation of the functionality, such as camera of the sensor blinded by newspaper or signal corrupted by electromagnetic interference.

The purpose of this analysis is to identify the improvements that need to be implemented to fulfil the safety constraints identified in the STPA. The triggering condition identified via STPA analysis shall be validated through dedicated test cases, which shall:

- Include an ID

- Include a brief description to describe the aim of the test itself

- Report step by step all the pertinent conditions and constraints to provide a comprehensive guide for the tester.

The validation of the triggering condition and the STPA analysis is contingent upon the successful outcome of each test case, with a test case being deemed successful if every step in it is successfully executed.

### 3.3. Example of V&V strategy application

This subsection presents the implementation of our proposed V&V strategy for the three use cases addressed in the SAFEXPLAIN project: automotive (led by NAVINFO), railway (IKERLAN), and aerospace (AIKO). To do so, this subsection follows the structure below for each of the previously mentioned use cases:

1. A description of scenarios extracted from the scenario catalogue (adapted to the three use cases), including their conditions/constraints.

2. A description of test cases at vehicle level and the expected behaviour at vehicle, sense, plan and actuator levels.

3. An example of triggering conditions derived from the previously identified hazards at vehicle level, including the associated control action, functional insufficiency and control action failure mode<sup>2</sup>.

4. An example of the related test case will be provided to validate the corresponding triggering condition (each triggering condition shall be validated by a related test case).

---

<sup>2</sup> This document presents a reduced version of the complete set of triggering conditions and related test cases development by EXIDA. The whole information has not been fully shared because of EXIDA's intellectually property restriction.

### 3.3.1. Automotive Use Case

This subsection focuses on the automotive use case developed by NAVINFO. It shall be noted that the content related to the scenario catalogue and the vehicle level test case in the automotive use case was previously reported in the [D2.1 deliverable](#); however, it has been included again for completeness, ensuring that examples for all SAFEXPLAIN applicable use cases are collected in one place.

#### 3.3.1.1. Example of Scenario from the scenario catalogue

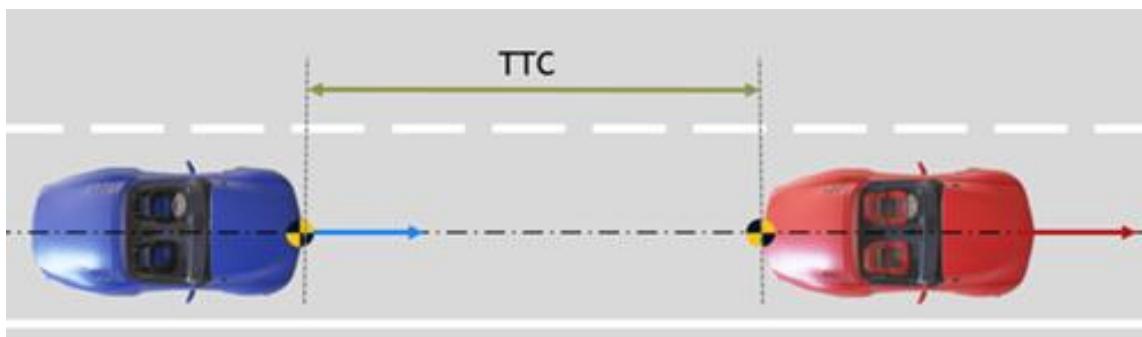

The scenario provided in this deliverable represents a vehicle driving following a target vehicle on highway, as depicted in Figure 3 (previously included in deliverable [D5.1](#)). When the distance with the target vehicle decreases so that the driver is in dangerous zone (possible collision) the intended functionality shall warn the driver and, if no driver reaction occurs and the collision is imminent, shall decelerate the vehicle.

Figure 3. Visual representation of the scenario example

The scenario conditions/constraints are the followings:

- The Ego vehicle (depicted in red in the Figure 3) drives with a longitudinal acceleration lower than  $2 \text{ m/s}^2$  towards a moving target vehicle (depicted in blue in the Figure 3) and is at a distance corresponding to a Time To Collision (TTC) of at least 4 s.

- The Ego vehicle speed range is [50 km/h, 130 km/h]

- The target vehicle drives at 80 km/h

- The following environmental conditions shall be present:

- Dry and daylight with minimum 1000 lux and Sun angle  $>15^\circ$  to horizon

- Dry and night with maximum 10 lux

- Road surface is asphalt or concrete.

- The following pre-conditions shall be respected:

- Both vehicles shall keep steady speed and path.

- Steering angle shall be lower than the override threshold.

- Yaw rate shall be lower than the override threshold.

- The probability of exposure (duration) of these scenario conditions is E2, considering the following combinations:

- Driving behind other vehicle with normal distance – E4 ( $>10\%$  of average operating time): E.g., 10% of 8000h = 800 h

- Driving with normal longitudinal acceleration ( $<2\text{m/s}^2$ ) – E4 ( $>10\%$  of average operating time): E.g., 10% of 8000h = 800 h

- Driving in Highway – E4 ( $>10\%$  of average operating time): E.g., 10% of 8000h = 800 h

### **3.3.1.2. Example of Vehicle level test case**

The following intended functionality capabilities shall be demonstrated:

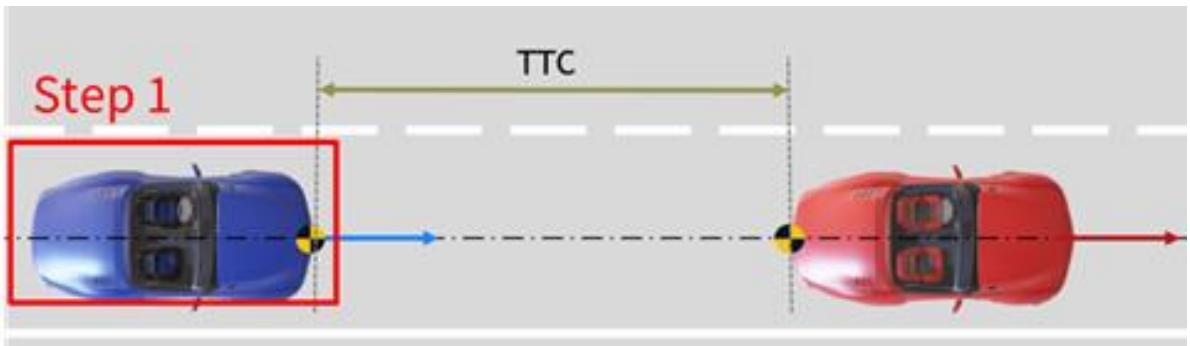

#### **3.3.1.2.1. Step 1.** Track the red target vehicle and evaluate it as no-collision relevant.

Figure 4. Vehicle level test case Step 1

Pass/Fail criteria:

- **Vehicle level:**

- Warning = It is not expected the provision of any warning to the driver.

- Braking = It is not expected the provision of braking intervention.

- **Sense level:**

- It is expected that the object is being detected and classified as a Car.

- **Logic level:**

- It is expected that the Object, considering the safety distance between the ego-vehicle and the target vehicle, is being evaluated as “no-collision” relevant.

- **Actuator level:**

- Warning = It is not expected the provision of any warning to the driver.

- Braking = It is not expected the provision of braking intervention.

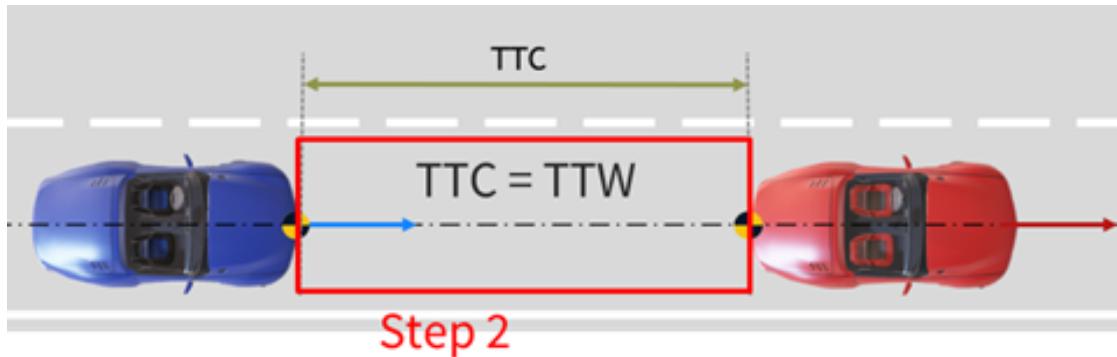

3.3.1.2.2. Step 2. When the distance, between the ego vehicle and the red target vehicle, is equal to the Time To Warning (TTW), the intended functionality shall evaluate the red target vehicle as collision relevant and provide at least 0,8 s before the start of the emergency braking the visual and audible warning to the driver (UN Regulation N° 152 clause 5.2.1.1, 5.5.1).

Figure 5. Vehicle level test case Step 2

Pass/Fail criteria:

- Vehicle level:

- Warning = It is expected the provision, at least 0,8 s before the start of the emergency braking according to UN Regulation N° 152 [13], of audible and visual warning to the driver.

- Braking = It is not expected the provision of braking intervention.

- Sense level:

- It is expected that the object is being detected and classified as a Car.

- Logic level:

- It is expected that the Object, considering that the safety distance between the ego-vehicle and the target vehicle is equal to TTW, is being evaluated as “collision” relevant.

- Actuator level:

- Warning = It is expected the provision, at least 0,8 s before the start of the emergency braking according to UN Regulation N° 152 [13], of audible and visual warning to the driver.

- Braking = For this step it is not expected the provision of braking intervention.

Note: UN Regulation N° 152 [13] is the Regulation applicable for the approval of vehicles of Category M1 and N1 with regard to an on-board system to:

- o Avoid or mitigate the severity of a rear-end in lane collision with a passenger car,

- o Avoid or mitigate the severity of an impact with a pedestrian.

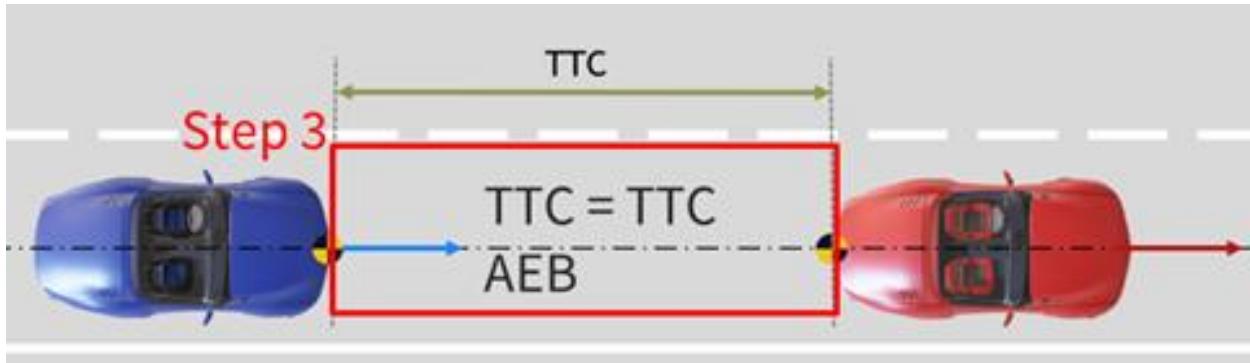

3.3.1.2.3. **Step 3**. When the distance, between the ego vehicle and the red target vehicle, is equal to the Time To Collision AEB (TTC AEB), the intended functionality shall, if no driver reaction occurs, shall decelerate the vehicle providing at least 5.0 m/s<sup>2</sup> (UN Regulation N° 152 clause 5.2.1.2).

Figure 6. Vehicle level test case Step 3

Pass/Fail criteria:

- Vehicle level:

- Warning = It is expected the provision, at least 0,8 s before the start of the emergency braking according to UN Regulation N° 152 [13], of audible and visual warning to the driver.

- Braking = It is expected a deceleration of at least 5 m/s<sup>2</sup>, according to UN Regulation N° 152 [13].

- Sense level:

- It is expected that the object is being detected and classified as a Car.

- Logic level:

- It is expected that the Object, considering that the safety distance between the ego-vehicle and the target vehicle is equal to TTC AEB, is being evaluated as "collision" relevant.

- Actuator level:

- It is expected the provision, at least 0,8 s before the start of the emergency braking according to UN Regulation N° 152 [13], of audible and visual warning to the driver.

- It is expected a deceleration of at least 5 m/s<sup>2</sup>, according to UN Regulation N° 152 [13].

### **3.3.1.3. From Hazard Vehicle Level to Triggering condition**

- Hazard Vehicle Level:

- AEB provides emergency braking when not needed

- Control Action:

- Perform emergency braking

- Control Action Failure Mode:

- Emergency braking is performed when the collision is not imminent

- Functional Insufficiency:

- The AEB reject an abortion request

- Triggering Condition:

- Abortion rejected by inaccurate throttle signal due to low communication buses performances (e.g. busy buses, inadequate message priority or arbitration or EMI)

- Abortion rejected by inaccurate steering signal due to low communication buses performances (e.g. busy buses, inadequate message priority or arbitration or EMI)

- Abortion rejected by wrong algorithm elaboration (wrongly evaluates the brake pedal status, the speed reduction reached by the vehicle, lateral acceleration value, yaw rate).

### **3.3.1.4. Example test case related to the triggering condition**

- Test ID: TCTC-01

- Tested Triggering Condition ID: TC2-0016

- Test Description: The test aims to verify whether the AEB is deactivated against a corrupted throttle signal due to low communication buses performance event.

- Test Steps:

- **Step 1:**

- Initial state:

- KI.15 = on

- No warning message available

- Intended functionality state: active

- Operating Element:

- Throttle Sensor System

- CAN Bus Simulator

- AEB ECU

- Operating:

- Sent valid throttle signal in time

- Expected Result:

- No warning message provided

- Intended functionality state: active

- **Step 2:**

- Initial state:

- KI.15 = on

- No warning message available

- Intended functionality state: active

- Operating Element:

- Throttle Sensor System

- CAN Bus Simulator

- AEB ECU

- Operating:

- Sent valid throttle signal in time

- Injected Emergency Braking Request

- Expected Result:

- Emergency Braking warning provided in time according to intended functionality requirement

- Emergency Braking Request provided in time according to intended functionality requirement

- Intended functionality state: active intervening

- Step 3:

- Initial state:

- KI.15 = on

- Emergency Braking warning provided

- Emergency Braking Request provided

- Intended functionality state: active intervening

- Operating Element:

- Throttle Sensor System

- CAN Bus Simulator

- AEB ECU

- Operating:

- After x ms it shall be sent a delayed throttle signal

- Expected Result:

- Intervention of dedicated CAN communication safety mechanism detecting the delay of throttle signal causing the deactivation of the functionality within x ms.

- Intended functionality state: deactivated.

### 3.3.2. Railway Use Case

This subsection implements the V&V strategy on an use case in the railway domain.

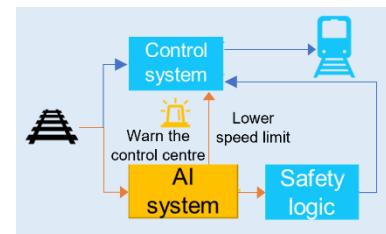

#### 3.3.2.1. Example of Scenario from the scenario catalogue

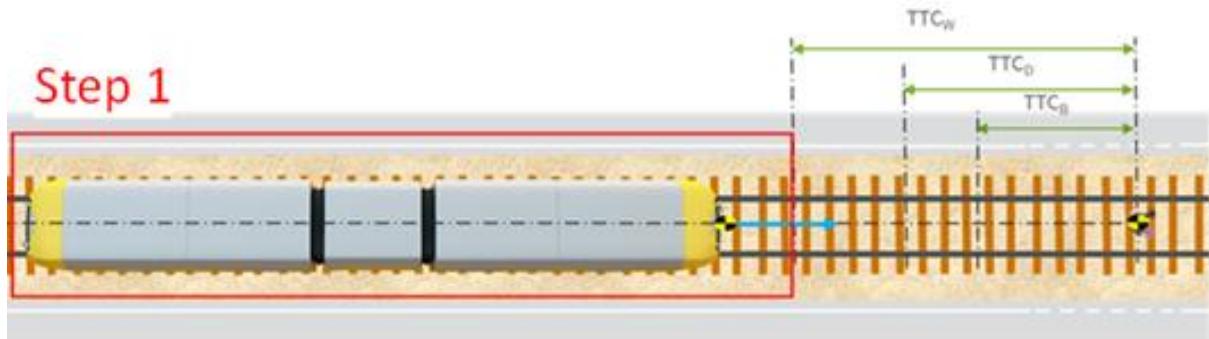

In this subsection is reported an example of one of the scenarios included in the scenario catalogue adapted to the Railway use case developed by IKERLAN. It represents a train that travels towards a static pedestrian on the tracks, as depicted in Figure 7.

Figure 7. Visual representation of the scenario example

When the distance with the pedestrian decreases so that the collision is possible, the intended functionality shall react as follow:

- If the distance with the pedestrian is equal to Time To Warning (TTC<sub>W</sub>) [1001 m, 1500 m], the intended functionality shall warn the driver about the upcoming collision.

- If the distance with the pedestrian is equal to Time To Deceleration (TTC<sub>D</sub>) [701 m, 1000 m], the intended functionality shall reduce the train speed through service brake intervention.

- If the distance with the pedestrian is lower to Time To Brake (TTC<sub>B</sub>) [700 m], the driver shall stop the train through emergency brake intervention.

The scenario conditions/constraints are the following:

- The train drives with a longitudinal acceleration lower than  $1\text{m/s}^2$  towards a pedestrian in the track and is at a distance of [0 m, 1500 m]

- The Train speed range is [0 km/h, 90 km/h]

- The speed limit in case the train goes in the station or out from the station shall be 30 km/h

- The speed limit in case the train is travelling outside the station shall be 90 km/h

- The pedestrian is stationary on the track

- The initial longitudinal offset is: 2000 m

- The maximum deceleration is:  $0,8\text{ m/s}^2$

- The following environmental conditions shall be present:

- Dry and daylight with 1500 lx as minimum luminosity range and Sun angle  $>15^\circ$  to horizon

- Rainy day with [0,1 mm/h, 7,6 mm/h] as rain intensity threshold and with [1000 lx, 1499 lx] as luminosity range

- Cloudy day with [1000 lx, 1499 lx] as luminosity range

- The following Pre-conditions shall be respected:

- Train shall keep steady speed

- no internal failure shall be present

### **3.3.2.2. Example of Vehicle level test case**

The following intended functionality capabilities shall be demonstrated:

#### **3.3.2.2.1. Step 1.** The train runs at constant speed on the track in the direction of the pedestrian.

Figure 8. Vehicle level test case Step 1

Pass/Fail criteria:

- TCS\_1 - Step 1 – Train

- Expected result:

- Warning = Not present

- Deceleration = Not present

- Braking = Not present

- TCS\_1 – Step 1 – Sense

- Expected result:

- No object detected

- TCS\_1 – Step 1 – Logic

- Expected result:

- No object detected (distance >  $TTC_W$ )

- TCS\_1 – Step 1 – Actuator

- Expected result:

- No warning triggered

- No deceleration actuated

- No braking actuated

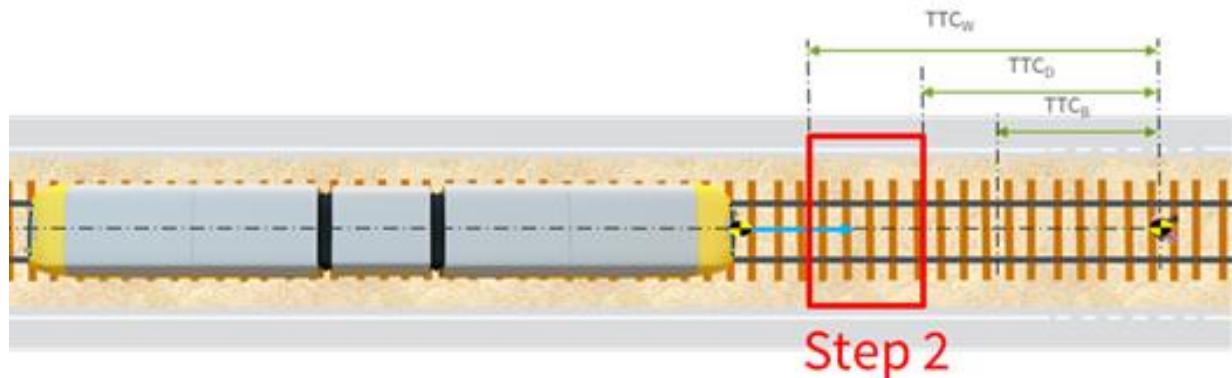

3.3.2.2.2. **Step 2.** When the distance between the train and pedestrian is equal to the  $TTC_W$ , the intended functionality shall evaluate the detected object (pedestrian), calculating its distance and collision probability and warn the driver about the pedestrian on the train path.

Figure 9. Vehicle level test case Step 2

Pass/Fail criteria:

- TCS\_1 - Step 2 – Train

- Expected result:

- Warning = Present

- Deceleration = Not present

- Braking = Not present

- TCS\_1 – Step 2 – Sense

- Expected result:

- Object detected

- Object classified as “pedestrian”

- Evaluate outputs of sensors to evaluate the expected results (e.g. detected objects, object classification)

- TCS\_1 – Step 2 – Logic

- Expected result:

- Object evaluated as “collision” relevant (distance  $> TTC_D > TTC_B$ )

- Evaluate outputs of Logic to evaluate the expected results (e.g. request to the actuator)

- TCS\_1 – Step 2 – Actuator

- Expected result:

- Warning triggered

- No deceleration actuated

- No braking actuated

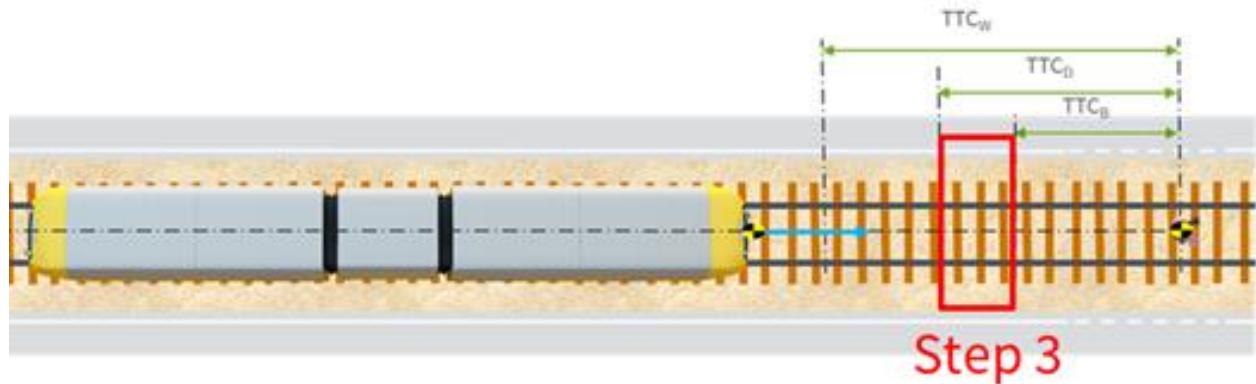

3.3.2.2.3. Step 3. When the distance between the train and pedestrian is equal to the  $TTC_D$ , the pedestrian is evaluated as critical and the intended functionality shall decelerate the train.

Figure 10. Vehicle level test case Step 3

Pass/Fail criteria:

- TCS\_1 - Step 3 – Train

- Expected result:

- Warning = Present

- Deceleration = Present

- Braking = Not present

- TCS\_1 – Step 3 – Sense

- Expected result:

- Object detected

- Object classified as “pedestrian”

- Evaluate outputs of sensors to evaluate the expected results (e.g. detected objects, object classification)

- TCS\_1 – Step 3 – Logic

- Expected result:

- Object evaluated as “collision” relevant (distance =  $TTC_D$ )

- Evaluate outputs of Logic to evaluate the expected results (e.g. request to the actuator)

- TCS\_1 – Step 3 – Actuator

- Expected result:

- Warning triggered

- Deceleration actuated

- No braking actuated

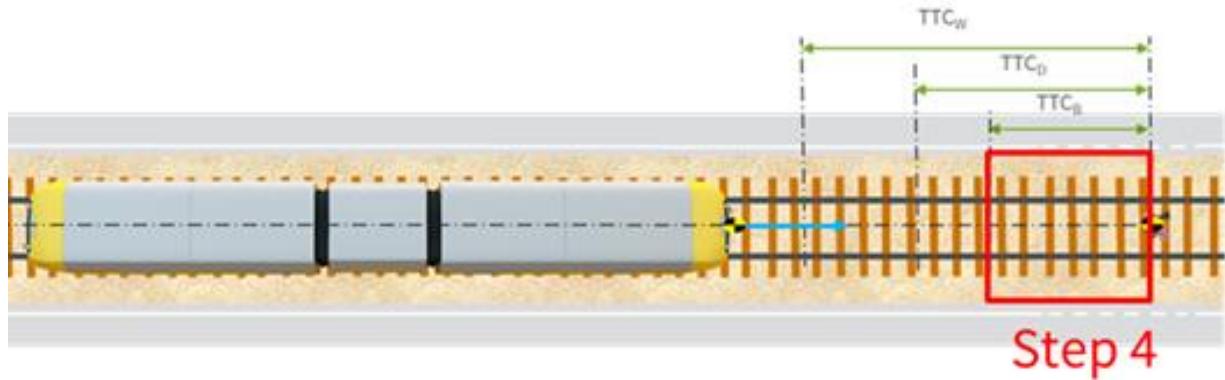

3.3.2.2.4. Step 4. When the distance between the train and pedestrian is equal to the  $TTC_B$ , the driver shall brake the train.

Figure 11. Vehicle level test case Step 4

Pass/Fail criteria:

- TCS\_1 - Step 4 – Train

- Expected result:

- Warning = Present

- Deceleration = Present

- Braking = Present

- TCS\_1 – Step 4 – Sense

- Expected result:

- Object detected

- Object classified as “pedestrian”

- Evaluate outputs of sensors to evaluate the expected results (e.g. detected objects, object classification)

- TCS\_1 – Step 4 – Logic

- Expected result:

- Object evaluated as “collision” relevant (distance =  $TTC_B$ )

- Evaluate outputs of Logic to evaluate the expected results (e.g. brake request to the driver)

- TCS\_1 – Step 4 – Actuator

- Expected result:

- Warning triggered

- Deceleration actuated

- No braking actuated

### **3.3.2.3. From Hazard Vehicle Level to Triggering condition**

- Hazard Vehicle Level:

- The ATO fails to warn the driver when required.

- Control Action:

- Warn the driver when a potential collision is imminent.

- Control Action Failure Mode:

- Warning not provided in a critical scenario.

- Functional Insufficiency:

- The ATO does not provide the warning.

- Triggering Condition:

- Warning is not provided to HMI ECU due to low buses communication.

- Missing object detection due to wrong camera position/camera calibration (e.g. The sensor is mounted in a wrong position/orientation leading to a missing object detection)

- Missing object detection due to camera low performances (e.g. damaged lens or undetected offline sensor)

- The logic responsible to elaborate the input data is stuck due to low computational power (e.g. low resources available).

### **3.3.2.4. Example test case related to the triggering condition**

- Test ID: TCTC-01

- Tested Triggering Condition ID: TC3-001

- Test Description: The test aims to verify whether the ATO is deactivated against a failure in the camera.

- Test Steps:

- **Step 1:**

- Initial state:

- KI.15 = on

- No warning message available

- Intended functionality state: active

- Operating Element:

- Camera Sensors

- CAN Bus Simulator

- ATO ECU

- Operating:

- Sent camera status signal to ATO ECU reporting that no failure is present

- Expected Result:

- No warning message provided

- Intended functionality state: active

- **Step 2:**

- Initial state:

- KI.15 = on

- No warning message available

- Intended functionality state: active

- Operating Element:

- Camera Sensors

- CAN Bus Simulator

- ATO ECU

- Operating:

- After x ms sent camera status signal to ATO ECU reporting that a failure is present

- Expected Result:

- Intervention of dedicated camera failure safety mechanism detecting the failure present in the camera causing the deactivation of the functionality within x ms.

- Intended functionality state: deactivated

### 3.3.3. Aerospace Use Case

The following subsection focuses on implementing the V&V strategy in the aerospace use case.

#### 3.3.3.1. Example of Scenario from the scenario catalogue

This subsection reports an example of one of the scenarios included in the scenario catalogue adapted to the aerospace use case developed by AIKO. It represents an Agent flies near a docking target and a black image is acquired due to a camera malfunction, as depicted in Figure 12.

Figure 12. Visual representation of the scenario example.

Description of the expect behaviour:

- When the agent flies in the Earth Orbit (LEO/GEO) close to a docking target, the acquired image is black (null image) due to a camera malfunction.

- As soon as a camera malfunction, which can lead to an incorrect execution of the functionality, is detected, the intended functionality shall provide a warning to the driver, and the functionality shall be deactivated.

The scenario conditions/constraints are the following:

- The agent flies towards a docking target and is at a distance corresponding to a Time To Collision (TTC) of at least 200 s.

- The agent relative speed range is [0 cm/s, 10 cm/s]

- Initial distance from the docking target: 15 m

- Camera is not working, and null image is acquired

- The following environmental conditions shall be present:

- Luminosity range: [1-30] (intensity of pixels in the image)

- Microgravity:  $ag = 8,8 \text{ m/s}^2$

- LEO (Low Earth Orbit)

- GEO (Geostationary Earth Orbit)

- The following Pre-conditions shall be respected:

- Camera acquires null image (black image) due to a camera malfunction.

### **3.3.3.2. Example of Vehicle level test case**

The following intended functionality capabilities shall be demonstrated:

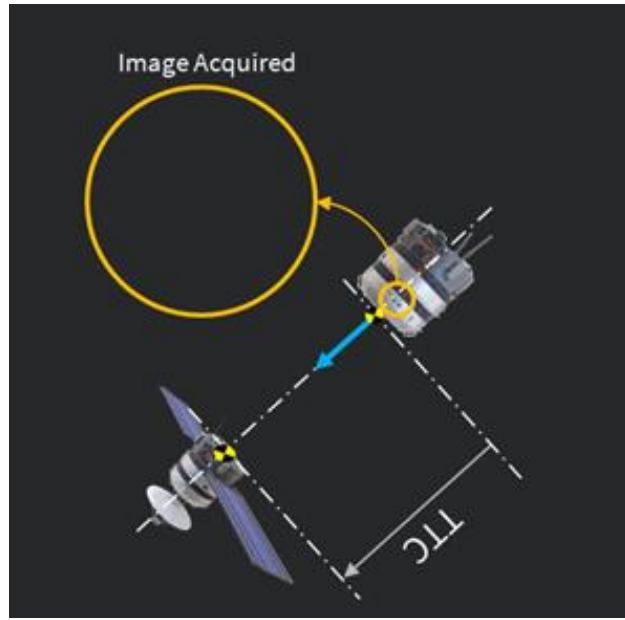

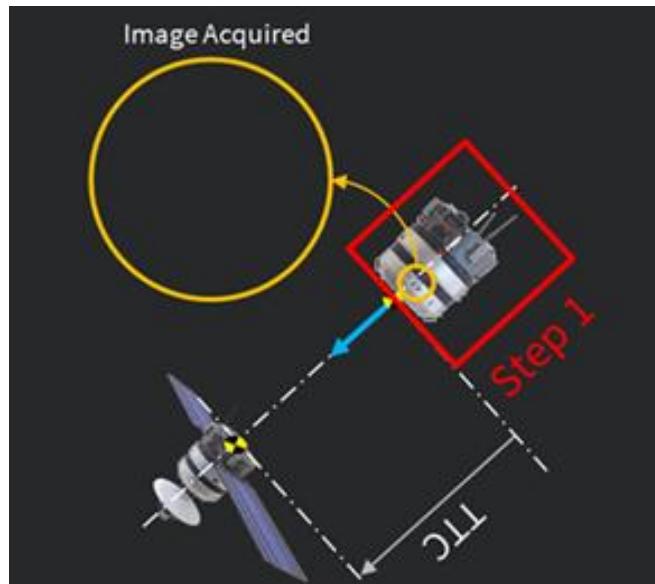

#### **3.3.3.2.1. Step 1.** As the agent flies along its own path, it approaches the target.

Figure 13. Vehicle level test case Step 1

Pass/Fail criteria:

- TCS\_2 - Step 1 – Agent

- Expected result:

- Target: Not detected

- Docking site: Not detected

- Docking operation relevant information: Not provided

- TCS\_2 – Step 1 – Sense

- Expected result:

- No object detected

- TCS\_2 – Step 1 – Logic

- Expected result:

- No object detected (distance > TTC)

- TCS\_2 – Step 1 – Human-Machine Interface (HMI)

- Expected result:

- Warning: Not triggered

- Docking operation relevant information: Not provided

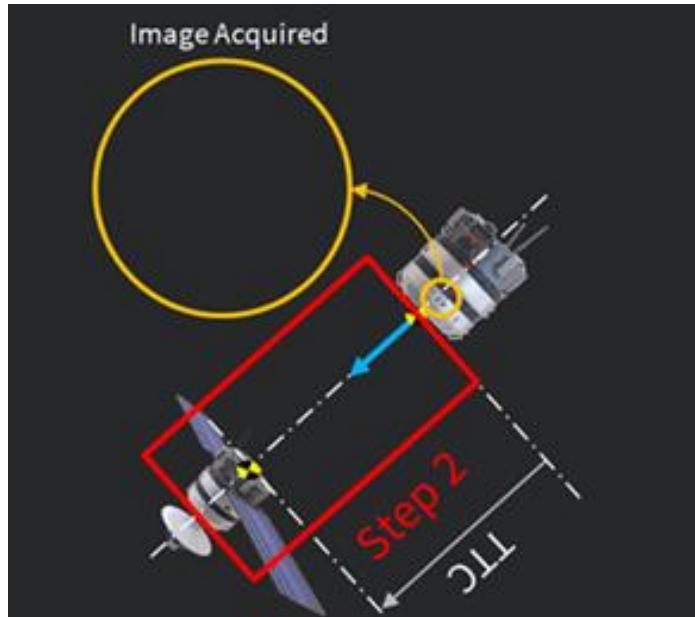

3.3.3.2.2. **Step 2**. When the distance between the agent and the target is equal to TTC, the intended functionality is not able to detect the target, since the acquired image is null (black) image due to a camera malfunction; the intended functionality shall provide a warning to the driver, and it shall be deactivated.

Figure 14. Vehicle level test case Step 2

Pass/Fail criteria:

- TCS\_2 - Step 2 – Agent

- Expected result:

- Warning: Provided

- TCS\_2 – Step 2 – Sense

- Expected result:

- No object detected

- Null image acquired

- TCS\_2 – Step 2 – Logic

- Expected result:

- Detection of malfunction in the camera

- TCS\_2 – Step 2 – HMI

- Expected result:

- Warning: Provided

### **3.3.3.3. From Hazard Vehicle Level to Triggering condition**

- Hazard Vehicle Level:

- The GNC System wrongly provide information related to the docking operation.

- Control Action:

- Information needed to docking operation are provided to the driver.

- Control Action Failure Mode:

- Wrong information related to the docking operation are provided to the driver.

- Functional Insufficiency:

- The GNC algorithm wrongly elaborate the received data.

- Triggering Condition:

- The decision algorithm wrongly elaborates the received signal, due to unknown signal.

- Missing detection of wrong input via plausibility check leads to incorrect agent position calculation.

- Wrong agent parameter estimation due to wrong camera position/camera calibration (e.g. the sensor is mounted in a wrong position/orientation).

- Agent parameters are wrongly estimated due to low computational power (e.g. overload).

### **3.3.3.4. Example test case related to the triggering condition**

- Test ID: TCTC-01

- Tested Triggering Condition ID: TC1-001

- Test Description: The test aims to verify whether the GNC System is deactivated against a received signal with an unknown value.

- Test Steps:

- **Step 1:**

- Initial state:

- KI.15 = on

- No warning message available

- Intended functionality state: active

- Operating Element:

- Camera Sensors

- CAN Bus Simulator

- GNC System ECU

- Operating:

- Sent camera signal to GNC System ECU with a valid value

- Expected Result:

- No warning message provided

- Intended functionality state: active

- **Step 2:**

- Initial state:

- KI.15 = on

- No warning message available

- Intended functionality state: active

- Operating Element:

- Camera Sensors

- CAN Bus Simulator

- GNC System ECU

- Operating:

- After x ms sent camera signal to GNC System ECU with unknown value

- Expected Result:

- Intervention of dedicated CAN communication safety mechanism detecting the unknown value of camera signal causing the deactivation of the functionality within x ms.

- Intended functionality state: deactivated

## 4. Acronyms and Abbreviations

Below is a list of acronyms and abbreviations employed in this document:

- AEB – Autonomous Emergency Braking

- AI – Artificial Intelligence

- ASPICE – Automotive SPICE

- DL – Deep Learning

- EASA – European Aviation Safety Agency

- Ego vehicle - vehicle fitted with functionality that is being analyzed for the SOTIF

- FSM – Functional Safety Management

- FuSa – Functional Safety

- GEO – Geostationary Earth Orbit

- HARA – Hazard Analysis and Risk Assessment

- II – Information Items

- ISO – International organization for standardization

- LEO – Low Earth Orbit

- ML – Machine Learning

- MLE – Machine Learning Engineering

- NN – Neural Network

- ODD – Operational Design Domain

- PAM – Process Assessment Model

- PRM – Process Reference Model

- QM – Quality Management

- QMS – Quality Management System

- SIL – Safety Integrity Level

- SOTIF – Safety Of the Intended Functionalities

- SPICE – Systems Process Improvement and Capability dEtermination

- SWE – Software Engineering

- TTC – Time To Collision

- TTW – Time To Warning

- VDA – Verband Der Automobil industrie

- V&V – Verification and Validation

- WP – Work Product

## 5. Bibliography

- [1] ISO, ISO 26262:2018 - Road vehicles — Functional safety, 2018..

- [2] ISO, ISO 21448:2022 Road vehicles — Safety of the intended functionality, 2022.

- [3] VDA 702, «Situationskatalog E-Parameter nach ISO 26262-3,» 2015.

## 6. Annexes

This section collects the annexes attached together with the deliverable D2.3.

### Annex A: Railway Safety Concept

This annex includes the document sent to the TÜV Rheinland certification entity to be reviewed.

### Annex B: Review meeting presentation

This annex collects the power point shared with TÜV Rheinland during the assessment of the Railway Safety Concept presented in the Annex A. In that presentation, the main set of review comments received from the TÜV Rheinland entity are included.

Safe and Explainable

Critical Embedded Systems based on AI

# Annex A: Railway Safety Concept

## Railway Safety Concept

Version 1.0

### Documentation Information

|                      |                                                          |

|----------------------|----------------------------------------------------------|

| Contract Number      | 101069595                                                |

| Project Website      | <a href="http://www.safexplain.eu">www.safexplain.eu</a> |

| Contractual Deadline | 31.03.2025                                               |

| Dissemination Level  | PU                                                       |

| Nature               | R                                                        |

| Author               | Irune Yarza, Irune Agirre                                |

| Contributors         |                                                          |

| Reviewer             | Ralf Röhrg (TÜV Rheinland)                               |

| Keywords             | Functional safety, AI, Railway                           |

This project has received funding from the European Union's Horizon Europe programme under grant agreement number 101069595.

## Change Log

| Version | Description Change              |

|---------|---------------------------------|

| V1.1    | TÜV Rheinland corrections       |

| V1.0    | Final version for TÜV Rheinland |

| V0.1    | First draft                     |

| V0.0    | Document created                |

|         |                                 |

|         |                                 |

|         |                                 |

|         |                                 |

# Table of Contents

|                                                                                 |    |

|---------------------------------------------------------------------------------|----|

| Change Log.....                                                                 | 2  |

| Table of Contents.....                                                          | 3  |

| Executive Summary .....                                                         | 5  |

| Structure of the document .....                                                 | 6  |

| Part I – Introduction (informative for TÜV Rheinland) .....                     | 7  |

| 1. Introduction.....                                                            | 8  |

| 1.1. Background .....                                                           | 8  |

| 1.1.1. AI-based systems.....                                                    | 8  |

| 1.1.2. NVIDIA Jetson AGX Orin .....                                             | 9  |

| 1.1.3. Standards and technical reports .....                                    | 9  |

| Part II – Reference safety architecture .....                                   | 11 |

| 2. Sources of Risk and Incremental Strategy .....                               | 12 |

| 2.1. AI Risk factors.....                                                       | 12 |

| 2.1.1. Functional Safety Standards.....                                         | 13 |

| 2.1.2. Technical reports on multicore integration (CAST-32A / AMC-20-193) ..... | 13 |

| 2.1.3. AI and FUSA Technical Reports (ISO/IEC TR 5469) .....                    | 14 |

| 2.1.4. Safety of The Intended Functionality (SOTIF) (ISO/DIS 21448).....        | 14 |

| 2.1.5. Summary of risk factors .....                                            | 14 |

| 2.2. Incremental strategy.....                                                  | 15 |

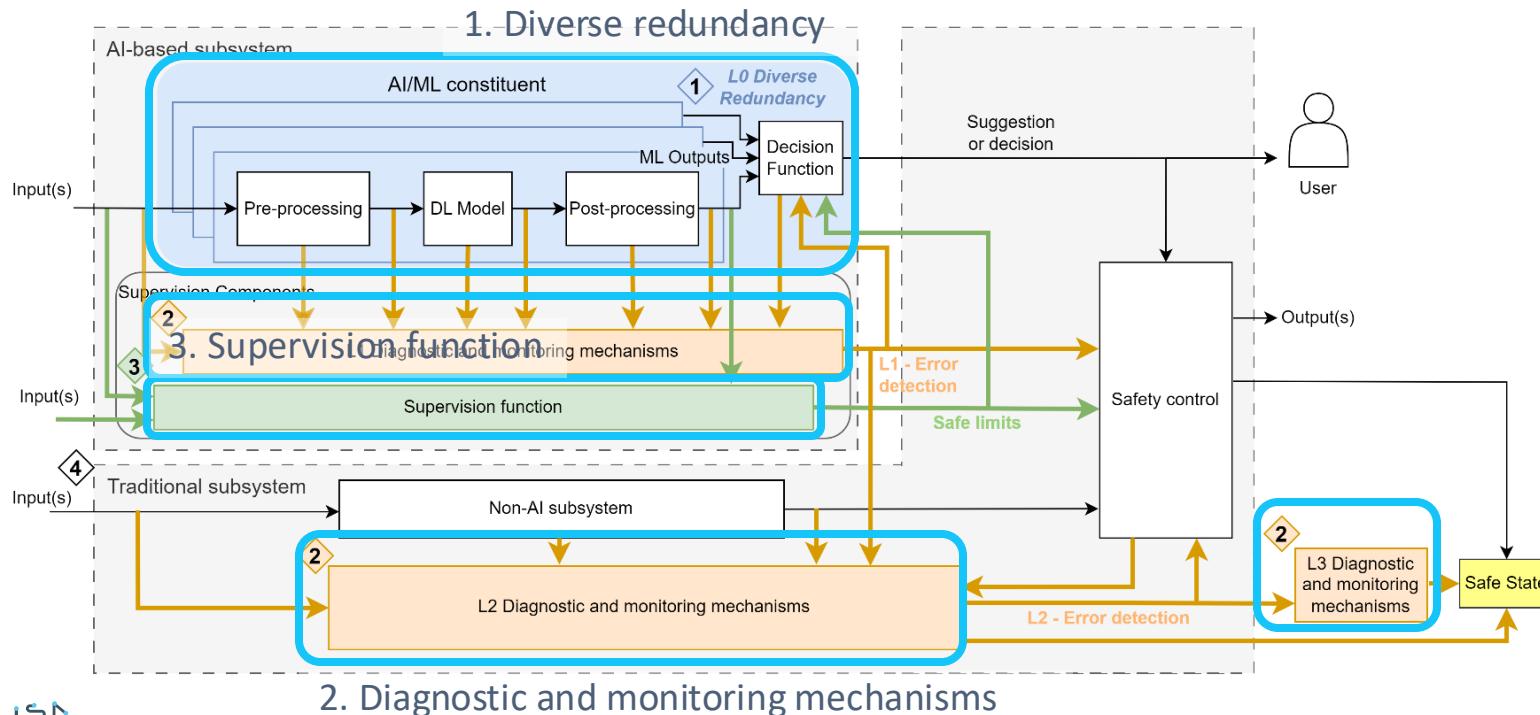

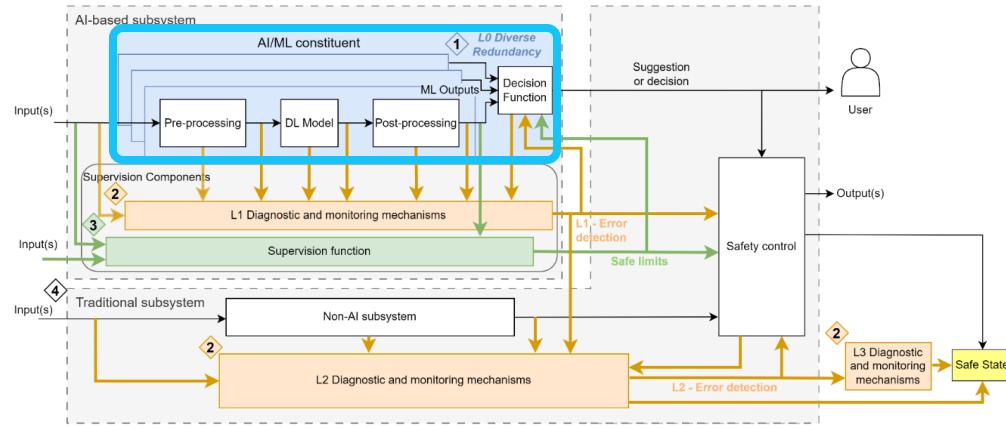

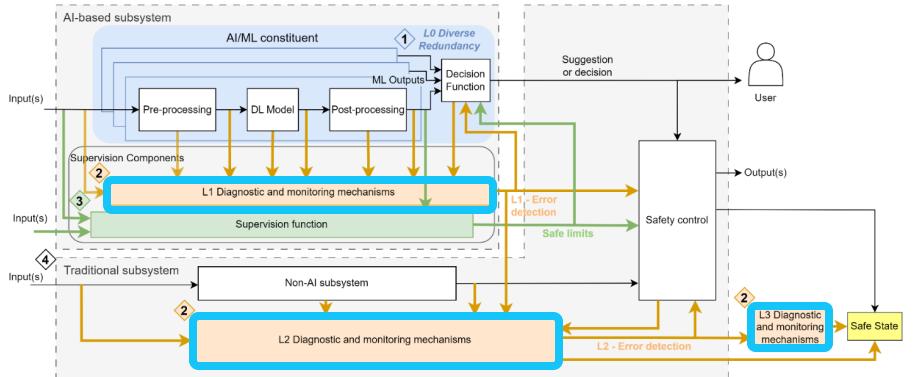

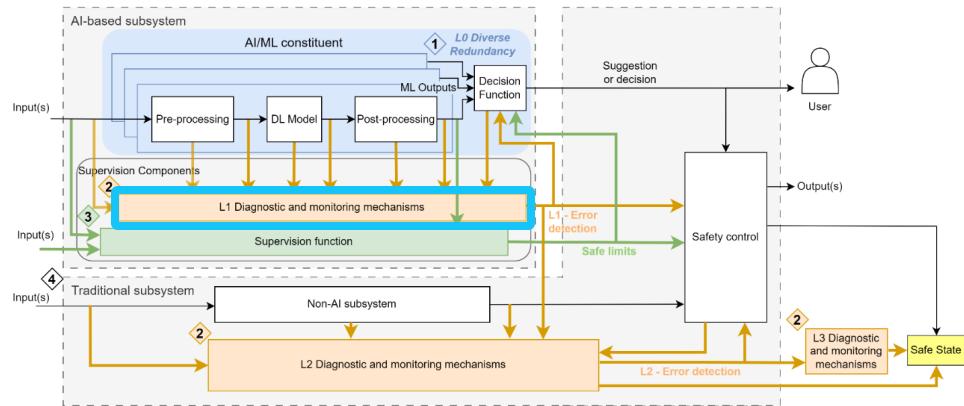

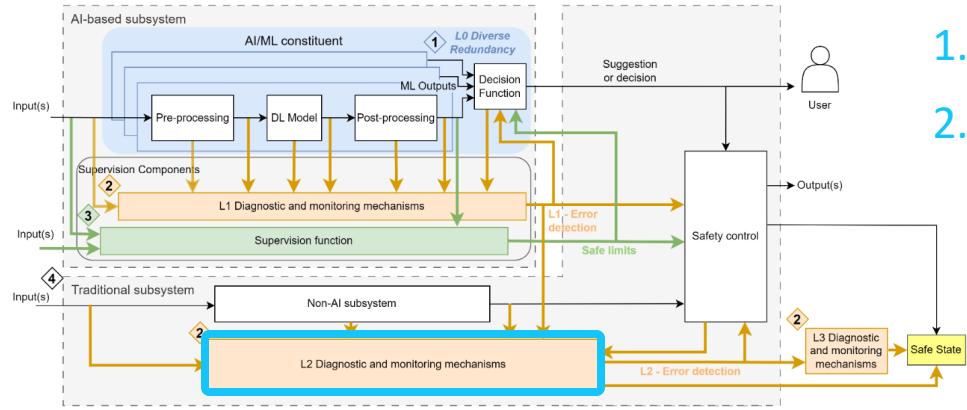

| 3. Reference architecture pattern .....                                         | 18 |

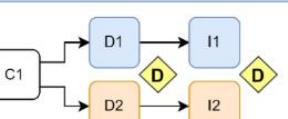

| 3.1. Diverse redundancy .....                                                   | 20 |

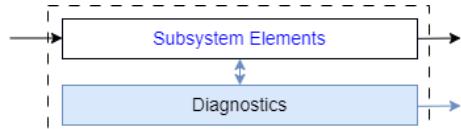

| 3.2. Diagnostic and Monitoring mechanisms .....                                 | 22 |

| 3.2.1. L1DM mechanisms – AI subsystem .....                                     | 23 |

| 3.2.2. L2DM mechanisms – Traditional subsystem.....                             | 24 |

| 3.2.3. L3 mechanisms – External .....                                           | 28 |

| 3.3. Supervision function .....                                                 | 28 |

| 3.4. Traditional subsystem.....                                                 | 28 |

| Part III – Railway case study .....                                             | 30 |

| 4. System concept specification .....                                           | 31 |

| 4.1. System description.....                                                    | 31 |

| 5. Safety Patterns.....                                                         | 34 |

|                                                   |    |

|---------------------------------------------------|----|

| 5.1. Safety Pattern 1 (SP1) .....                 | 34 |

| 5.1.1. System Architecture .....                  | 34 |

| 5.1.2. Diagnostic and monitoring mechanisms ..... | 35 |

| 5.2. Safety Pattern 2 (SP2) .....                 | 39 |

| 5.2.1. System Architecture .....                  | 39 |

| 5.2.2. Diverse redundancy .....                   | 40 |

| 5.2.3. Diagnostic and monitoring mechanisms ..... | 41 |

| 5.3. Safety Pattern 3 (SP3) .....                 | 43 |

| 5.3.1. System Architecture .....                  | 43 |

| Acronyms and Abbreviations .....                  | 46 |

| References .....                                  | 47 |

## Executive Summary

Deep Learning (DL) techniques are at the heart of most future advanced software functions in Critical Autonomous AI-based Systems (CAIS), where they also represent a major competitive factor. Hence, the economic success of CAIS industries (e.g., automotive, space, railway) depends on their ability to design, implement, qualify, and certify DL-based software products under bounded effort/cost. However, there is a fundamental gap between Functional Safety (FUSA) requirements on CAIS and the nature of DL solutions. This gap stems from the development process of DL libraries and affects high-level safety concepts such as (1) explainability and traceability, (2) suitability for varying safety requirements, (3) FUSA-compliant implementations, and (4) real-time constraints. As a matter of fact, the data-dependent and stochastic nature of DL algorithms clashes with current FUSA practice, which instead builds on deterministic, verifiable, and pass/fail test-based software.

The SAFEXPLAIN project tackles these challenges and targets by providing a flexible approach to allow the certification – hence adoption – of DL-based solutions in CAIS building on: (1) DL solutions that provide end-to-end traceability, with specific approaches to explain whether predictions can be trusted and strategies to reach (and prove) correct operation, in accordance to certification standards; (2) alternative and increasingly sophisticated design safety patterns for DL with varying criticality and fault tolerance requirements; (3) DL library implementations that adhere to safety requirements; and (4) computing platform configurations, to regain determinism, and probabilistic timing analyses, to handle the remaining nondeterminism.

This document provides strategies and specific solutions to realize safety patterns for safety-relevant software systems that include Artificial Intelligence (AI) software components. Moreover, the proposed architectural solution is tailored to a railway case study for its assessment with respect to safety certification by means of a safety concept.

Future exploitation of the main SAFEXPLAIN concepts, architecture and solutions could be at stake if no clear route for certification is identified, which can accompany industrial interest. Additionally, to ensure that relevant certification bodies with authority in the targeted domains are aware of the SAFEXPLAIN approach is also a key interest of the project.

This self-contained document is submitted to TÜV Rheinland, a relevant certification body in the industrial domain, with the following goals:

- The third-party authoritative review report on the suitability of the research concepts of SAFEXPLAIN, identifying possible implausibilities of the approach or possible contradictions with requirements of the Bases of Assessment and evaluating the use of the approach in the context mentioned.

- The dissemination of SAFEXPLAIN contribution to TÜV Rheinland.

- The gathering of detailed feedback from TÜV Rheinland.

- The definition of an action plan based on the received feedback (if needed).

- The suggestion of updates to the current standards or certification processes (where needed).

## Structure of the document

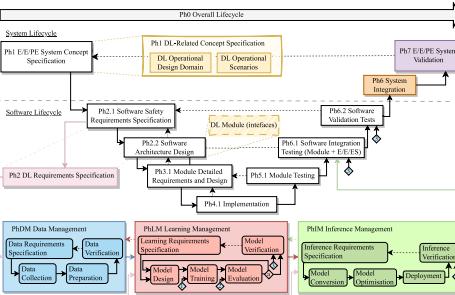

This document is organized in three main parts:

- **Part I – Introduction (informative):** This part serves solely introductory purposes and hence, it is not intended for review. Section 1 provides a basic background on the SAFEPLAIN project and certification standards, focusing on the main topic of the project: Artificial Intelligence (AI) based systems, NVIDIA Jetson AGX Orin (target HW platform) as well as standards and technical reports.

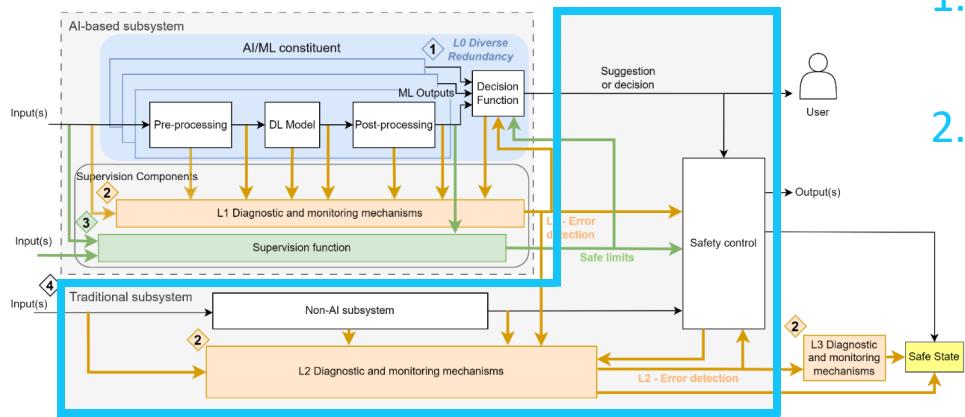

- **Part II – System architecture (to be reviewed):** This part describes the reference safety architecture and safety patterns to be reviewed by TÜV Rheinland:

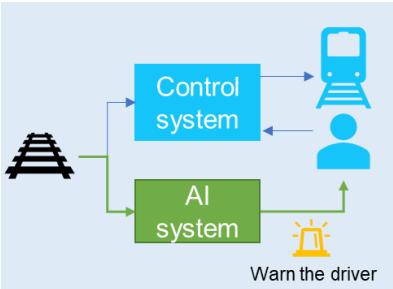

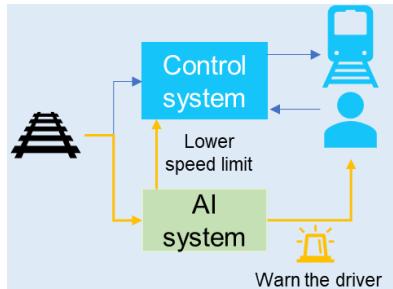

- Section 2 reviews the relevant sources of risk for AI-based solutions in safety-critical systems, including AI-related factors and traditional ones. Then, section 2.2 reviews the different usage and automation levels for DL solutions, and how they are tackled incrementally in the project, and also in this document.

- Section 3 provides the general structure of the safety patterns, as well as the techniques considered for diverse redundancy, diagnostics, monitoring, and supervision in the different safety patterns.

- **Part III – Railway case study (to be reviewed):** This part tailors the reference safety architectural pattern to a railway case study.

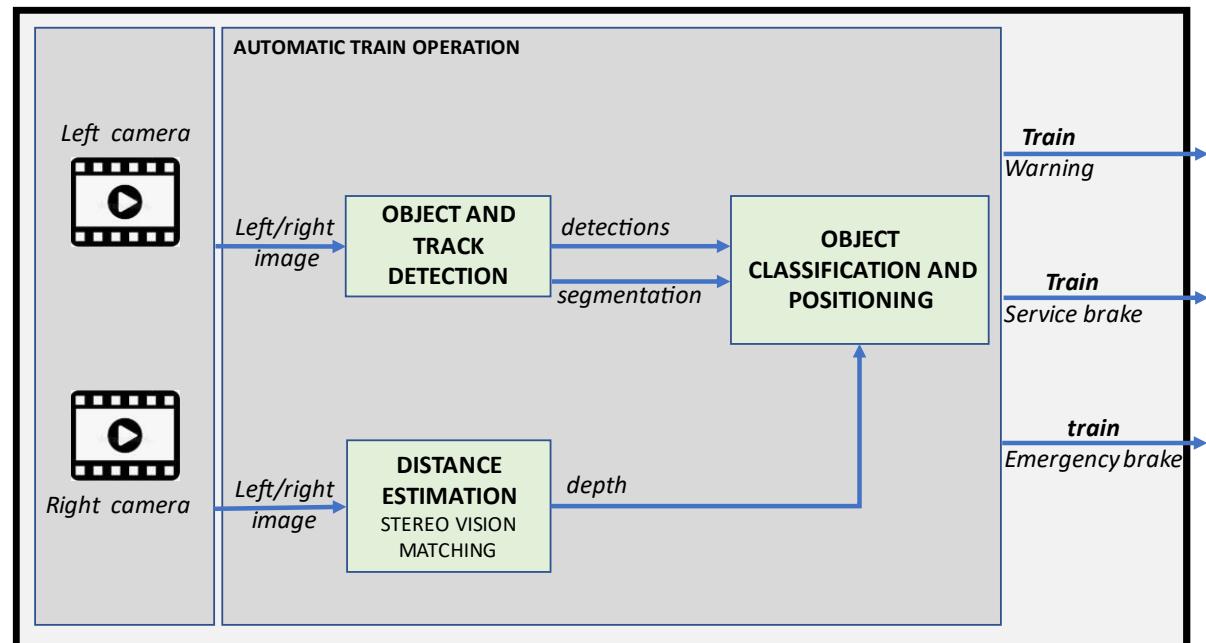

- Section 4 presents the railway case study, which consists of a railway domain object detector controller for an Automatic Train Operation (ATO) system. Aiming an incremental adoption of AI in the system, several situations have been considered, where the AI system plays different roles within the ATO system.

- Section 5 instantiates the general pattern for specific usage and automation levels, reviews the relevant techniques to be used for diverse redundancy, diagnostics, monitoring, and supervision for each of the patterns, and provides guidance on how to map those solutions to the target platform of the project (NVIDIA Orin).

# Part I – Introduction (informative for TÜV Rheinland)

# 1. Introduction

Systems with safety requirements follow a development process that leads to architectures that allow satisfying those requirements. Those architectures have a large set of commonalities across different systems with comparable safety requirements, and hence, a number of safety patterns have been developed in each application domain as a way to generate specific architectures reusing previous efforts to reduce costs and risks. One such example of safety pattern is the E-gas Concept (EGAS Workgroup, 2013) used in the automotive domain, which is the basis for the architecture of many automotive systems with limited integrity levels (e.g., ASIL-A or ASIL-B according to ISO 26262 (International Standardization Organization, 2018)).

However, AI-based software has a number of characteristics that clash with those expected for safety-relevant software, such as a pseudo stochastic behaviour with non-guaranteed correct outputs, and a data-based software design rather than being a purely control algorithm. Hence, traditional safety patterns cannot be applied as they are, and new ones need to be devised.

In this section, we provide some context and scope to the problem of developing AI-based software architectures with safety requirements and provide some background on the relevant safety regulations and the target platform where those software architectures have to be deployed.

## 1.1. Background

This section provides background on the main concepts used in this report: nomenclature on AI-based systems, the main features of NVIDIA Jetson AGX Orin platform where the safety patterns will be applied, and a recall of the safety standards used as reference.

### 1.1.1. AI-based systems

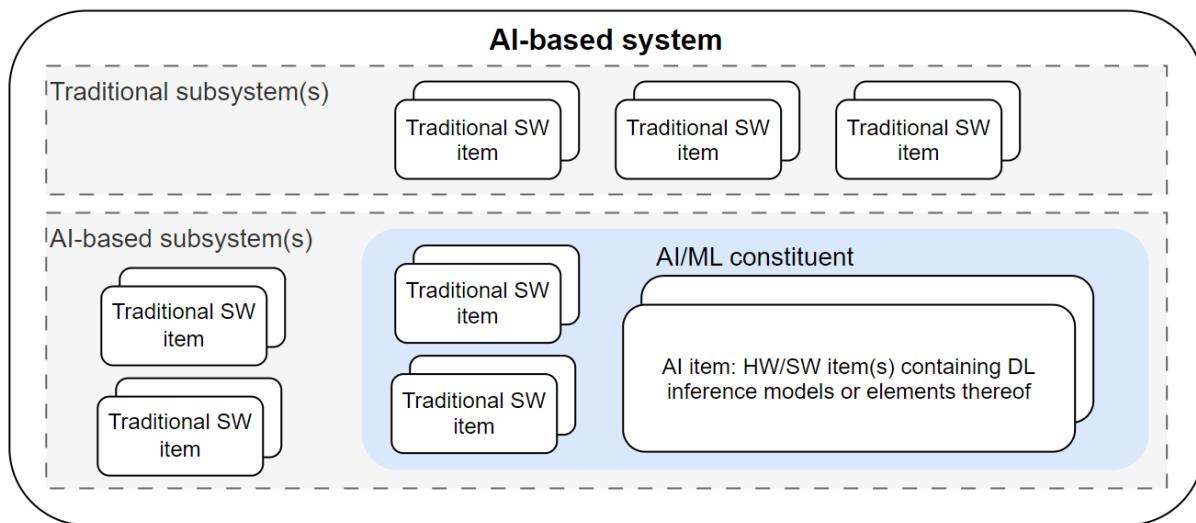

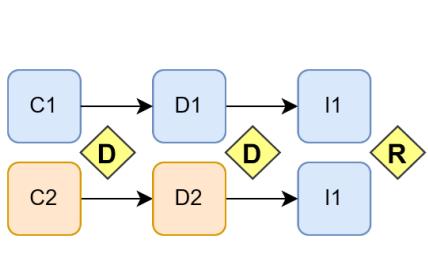

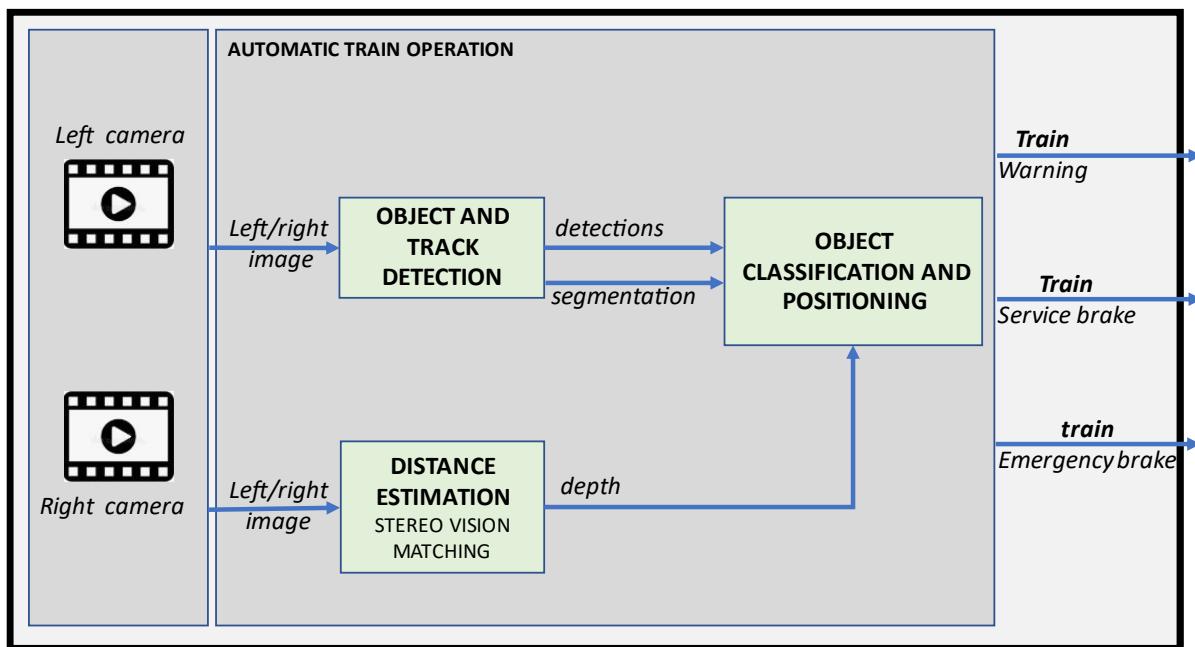

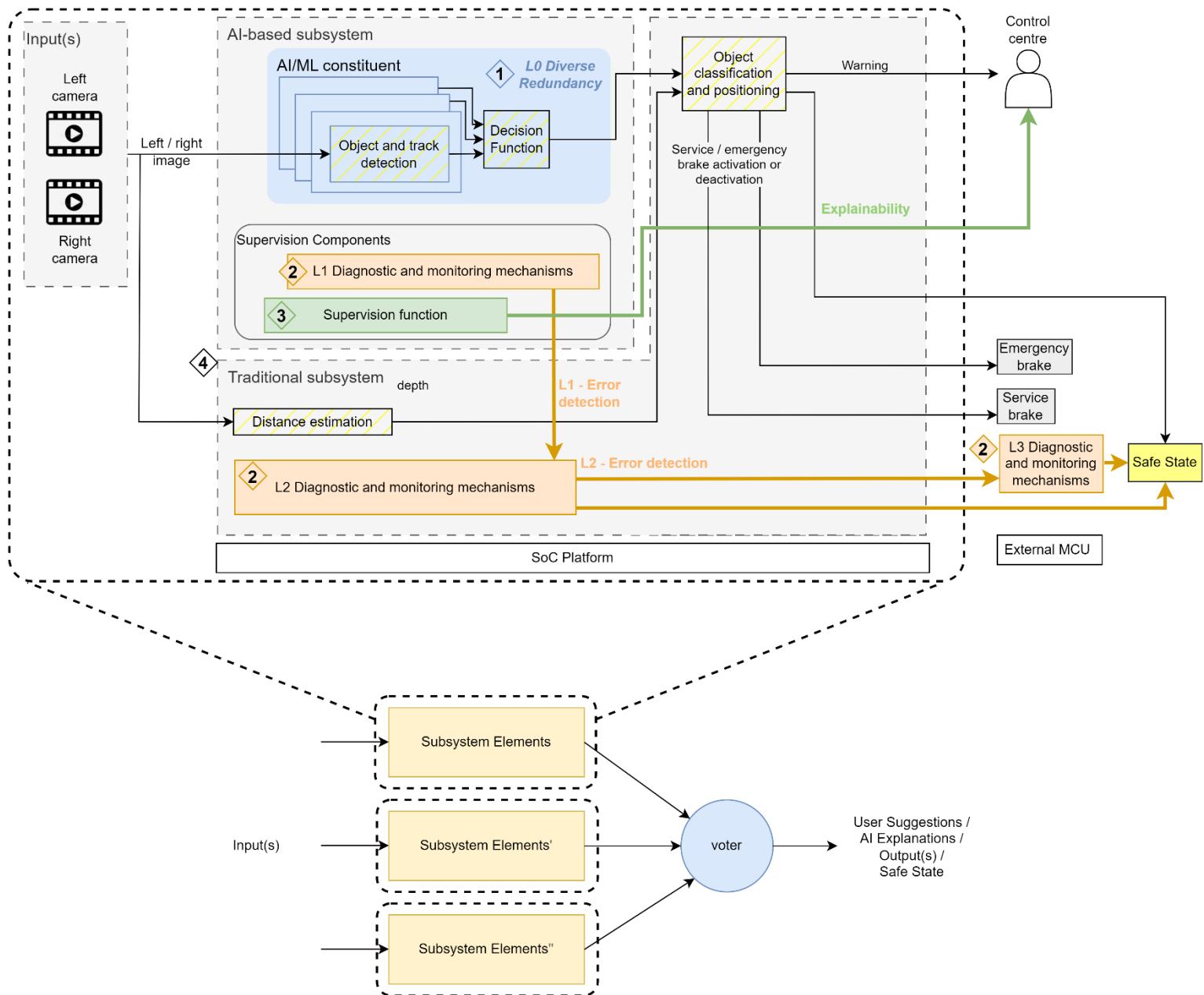

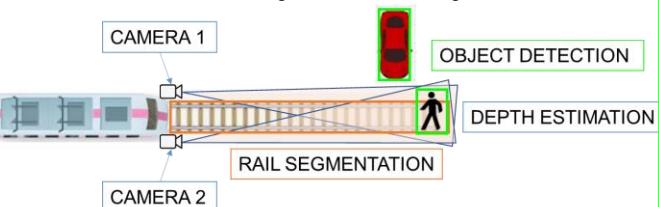

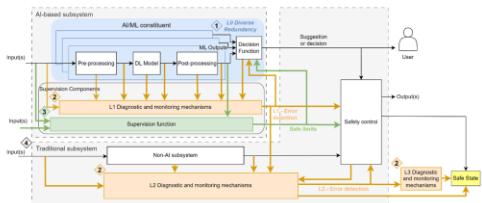

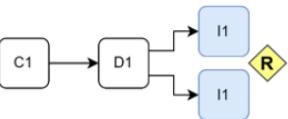

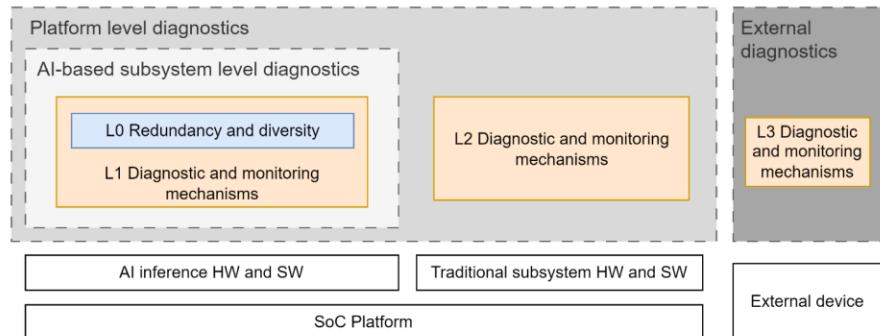

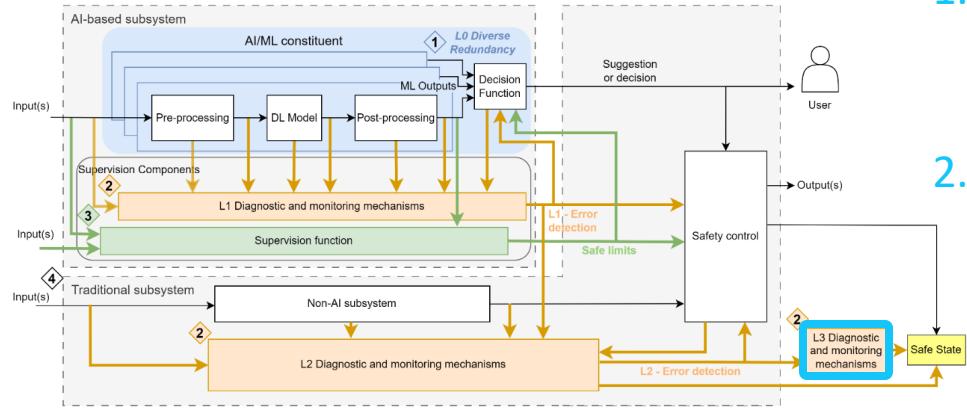

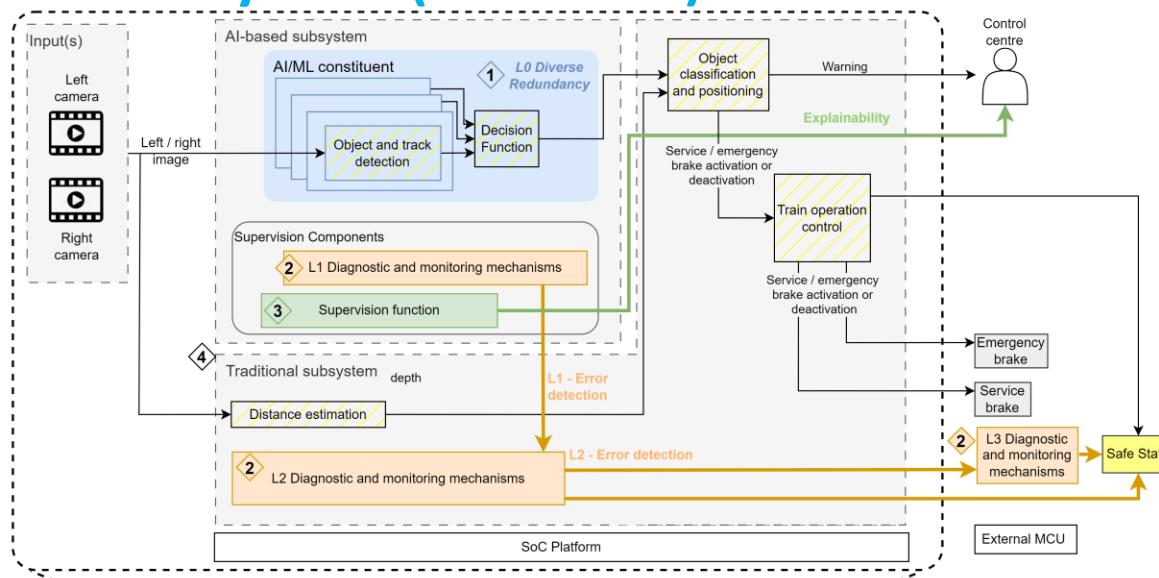

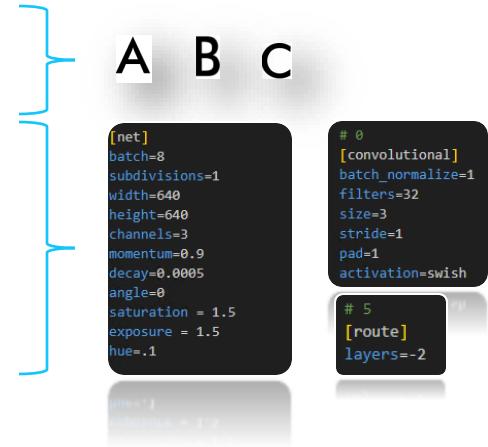

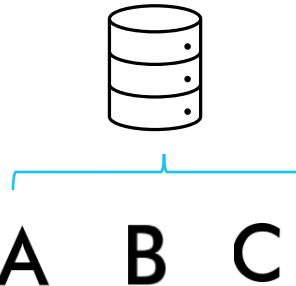

When referring to AI-based safety systems, this report considers the definitions of the European Aviation Safety Agency (EASA) concept paper for Machine Learning (ML) application [1], which makes the decomposition shown in Figure 1.

Based on this decomposition, the EASA concept paper makes the following definitions:

- AI-based system: systems encompassing traditional subsystem(s) and incorporating at least one AI-based subsystem.

- AI-based subsystem: subsystem that involves one or more AI/ML constituents.

- AI/ML constituent: It is a combination of software and hardware items that include at least one specialized hardware or software item containing at least one ML model.

- AI/ML item: specialized hardware or software item that builds the ML model(s). In particular, we focus on Deep Learning (DL) models, a subfield of ML.

- Traditional subsystem: subsystem that does not include any ML model.

- Traditional SW/HW item: hardware or software items that do not include ML model(s).

This safety concept focuses on AI/ML constituents with the following features:

- Deep Learning (DL) algorithms based on supervised learning for visual perception classification tasks.

- Applications based on offline learning processes in which the model remains fixed at approval time, while excluding online learning processes.

Figure 1: Artificial Intelligence (AI)-based system decomposition based on EASA concept paper [1]

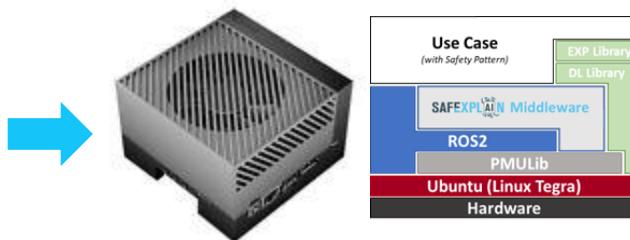

### 1.1.2. NVIDIA Jetson AGX Orin

The target MPSoC platform in SAFEPLAIN belongs to the NVIDIA Jetson AGX Orin family. In SAFEPLAIN, the AGX Orin Dev Kit has been selected. The Orin comprises 3 clusters of 4 Arm Cortex-A78AE CPUs, a dual core Sensor Processing Engine (SPE), which can be configured in lockstep mode, a NVIDIA Ampere GPU, ad-hoc AI-oriented accelerators, and a video encoder / decoder.

Clusters based on Arm cores provide general purpose computing capabilities suitable for control software and software components around AI-based software, but without needing AI-specific support or massively parallel hardware components. Each of the three clusters includes four cores that can be used as either 4 independent cores, or as 2 pairs of lockstep cores. Cores include local (L1 and L2) caches. There is a L3 cache shared across all cores in the cluster, but it includes partitioning support. We refer to the set of 3 core clusters as CCPLEX for short.

Computing devices like the GPU and the AI-oriented accelerators have a complementary nature to the core clusters and are suitable for AI software and other embarrassingly parallel software. In particular, the GPU has a number of Stream Multiprocessors (SMs) sharing a L2 cache, which, apparently, cannot be partitioned.

Core clusters and the GPU share a L4 cache that, so far, cannot be partitioned, and hence, both cores and the GPU share it. However, we note that, due to its limited size, does not seem to be intended for providing increased cache space for the L3 caches of the core clusters or the L2 cache of the GPU.

### 1.1.3. Standards and technical reports

Although this safety concept is focused on a railway domain case study, the outcomes of this project are meant to be cross-domains, therefore, the following domain independent standards are taken as basis:

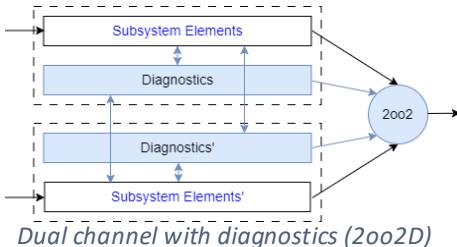

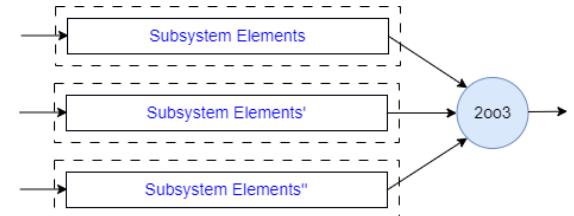

- **IEC 61508:2010 - Functional safety of electrical/electronic/programmable electronic safety-related systems [2]:** Traditional FUSA architectural safety patterns from this standard are used as starting point for the definition of reference architecture of Section 3 in this report.

- **ISO/IEC TR 5469:2024 - Artificial intelligence — Functional safety and AI systems** [3]: Section 2.2 explains the definition of the different DL usage levels according to ISO/IEC TR 5469 which is used as the basis for the incremental strategy of this report and the architectural safety patterns for AI presented in Section 5.

In addition to these domain independent standards, technical reports from different domains are also taken as reference:

- **CAST-32A and AMC-20-193 from the avionics domain for multicore processors** [4]: these two technical reports from the avionics domain provide guidance on the adoption of multicore processors for critical systems. Many of the principles described there are also applicable to HPEC platforms that integrate multicore processors together with additional accelerators and diverse computing resources.

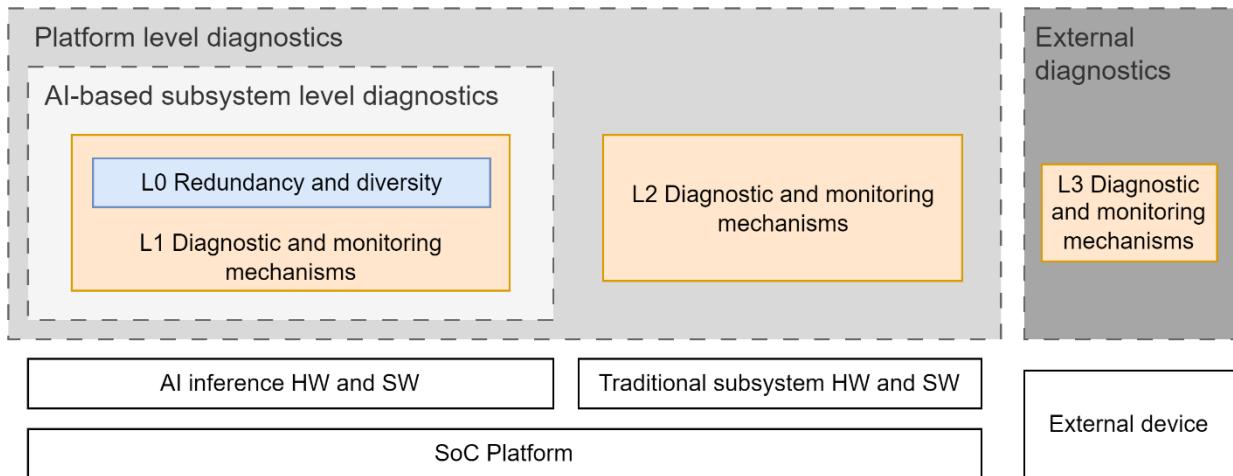

- **E-Gas architecture concept from the automotive domain** [5]: The E-Gas architecture concept, defined by the German Association of the Automotive Industry (VDA), has the aim to standardize the safety architecture for engine control systems. The defined architecture is in compliance with ISO 26262 and it can be applied as a well-trusted design principle. The E-Gas defines a 3-level monitoring concept that has been used as reference in this report (Section 3.2), adapting it to AI systems particularities and to ISO/IEC TR 5469.

## Part II – Reference safety architecture

## 2. Sources of Risk and Incremental Strategy

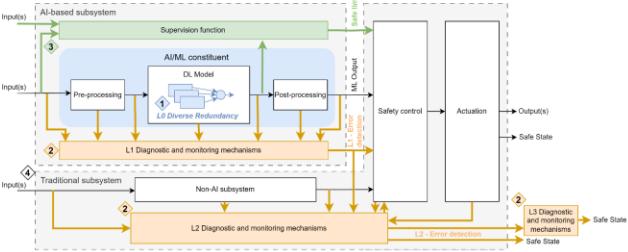

In order to define the safety architecture patterns, first main problems arising from the use of AI in safety critical systems and their root causes are analysed and then an incremental strategy to deal with them is defined.

### 2.1. AI Risk factors

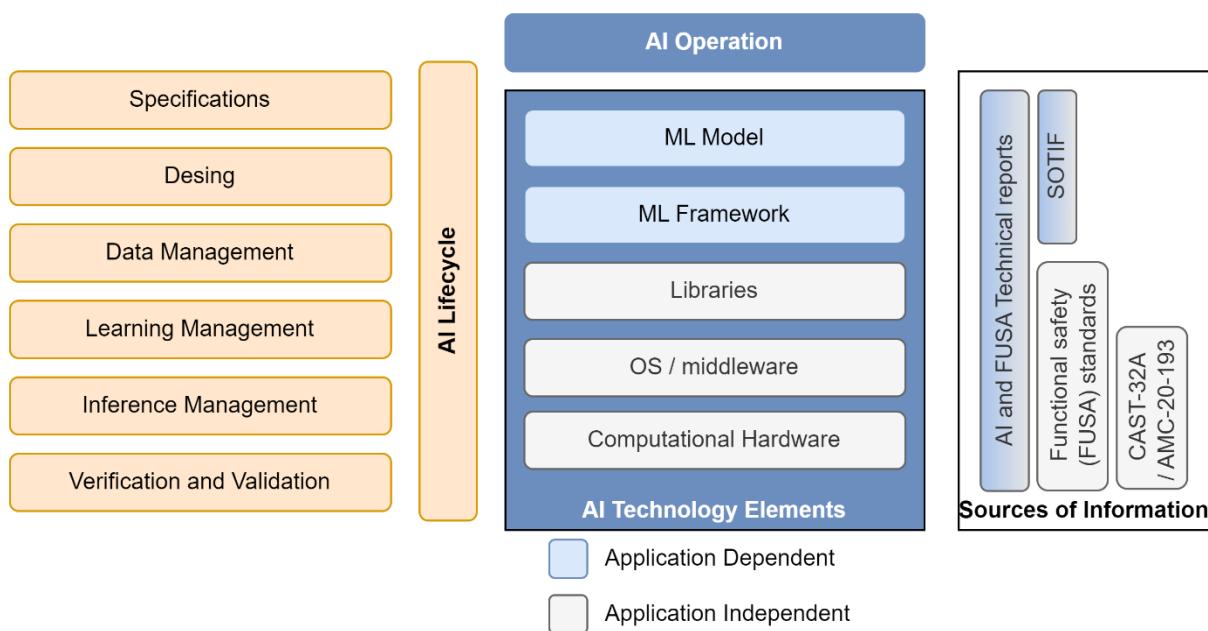

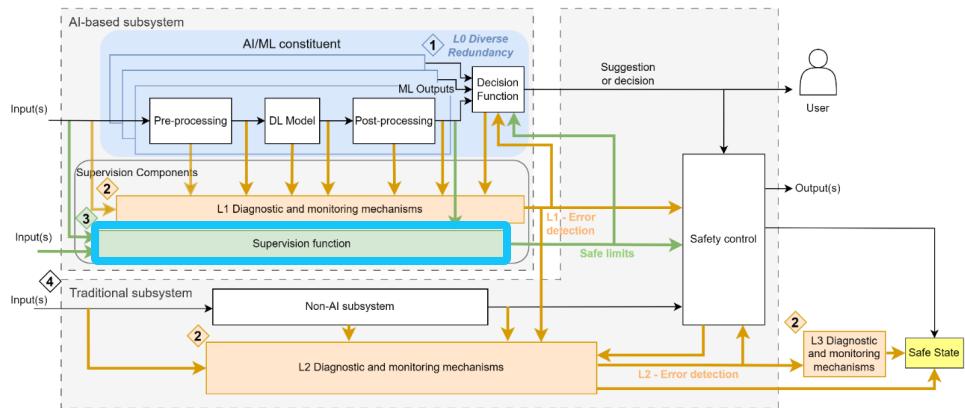

As for traditional safety related systems, the main risk factors related to AI-based systems can be originated either in its development or at operation. Figure 2 depicts this classification criteria together with information sources used in this section to identify the different risk factors. During the development, there are several stages at which systematic faults can originate, like incomplete specifications, biased training data or wrong design decisions affecting the ML model. In order to reduce the probability of systematic faults in the AI-based subsystem, safety considerations shall be taken in the AI lifecycle. In SAFEEXPLAIN this has been addressed by the AI-FSM [6] and hence, this report does not focus on the risk factors originated in the AI lifecycle but on the AI Operation instead. However, the high complexity of AI systems makes it very difficult to mitigate all systematic faults through design and verification and validation processes, and it is assumed that residual systematic faults will manifest at operation and should be covered by the runtime mechanisms in the safety architecture too, as done for random faults.

Figure 2: AI Risk factor classification and sources of information

At operation time, residual systematic faults and random faults can impact different elements of the AI-subsystem, this determines the architectural measures required for runtime error detection and monitoring. Based on ISO/IEC TR 5469 we classify these AI technology elements in the 5 groups shown in Figure 2:

- Application Independent: The lowest levels of the AI technology elements can be considered as application independent:

- Computational Hardware: refers to the hardware platform and its processing units (e.g., CPU, GPU, Accelerators).

- OS / middleware: This component is not included in ISO/IEC TR 5469, but many faults could also originate on this layer.

- Libraries: ML components often require specific libraries for their inference (e.g., cudNN). These libraries can also be implemented in different programming languages such as CUDA, C, C++, python...

- Application dependent: Higher levels of the AI technology elements are usually platform dependent:

- ML framework: many different frameworks can be used depending on the application that is being implemented (e.g., TensorFlow, Pytorch, Keras).

- ML model: the ML model will depend on the specific application and the design decisions taken for it (architecture, hyperparameters, number of layers, etc).

The analysed sources for identifying relevant risk factors on AI operation cover different AI technology elements as explained in next subsections.

### 2.1.1. Functional Safety Standards

Functional safety standards such as IEC 61508, ISO 26262 or EN 5012x only address the application independent technology elements from Figure 2 (computational hardware and software) as they do not address AI-specific topics. According to ISO / IEC TR 5469 these technology elements can be addressed through existing functional safety concepts following IEC 61508-2 for hardware and IEC 61508-3 for software. However, for elements containing AI technology (ML model and related tools) a set of new properties, listed in Section 2.1.3, are defined.

Traditional functional safety standards classify failures based on their origin as systematic or random:

- **Systematic failure:** “failure, related in a deterministic way to a certain cause, which can only be eliminated by a modification of the design or of the manufacturing process, operational procedures, documentation or other relevant factors” from IEC 61508-4.

- **Random hardware failure:** “failure, occurring at a random time, which results from one or more of the possible degradation mechanisms in the hardware” from IEC 61508-4.

Concerning systematic faults affecting AI SW development (lifecycle) it is an open research topic that has been explored by several research papers. Humbatova et al. [7] introduce a large taxonomy of faults in DL systems' development using several frameworks. Moreover, Schnitzer et al. [8] propose a framework for the systematic management of risks associated with AI. This framework builds upon an AI hazard list from a SoA analysis.

### 2.1.2. Technical reports on multicore integration (CAST-32A / AMC-20-193)

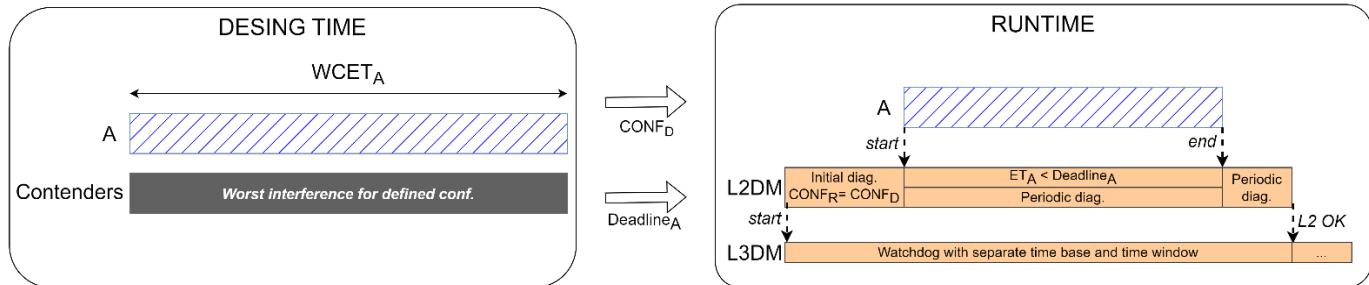

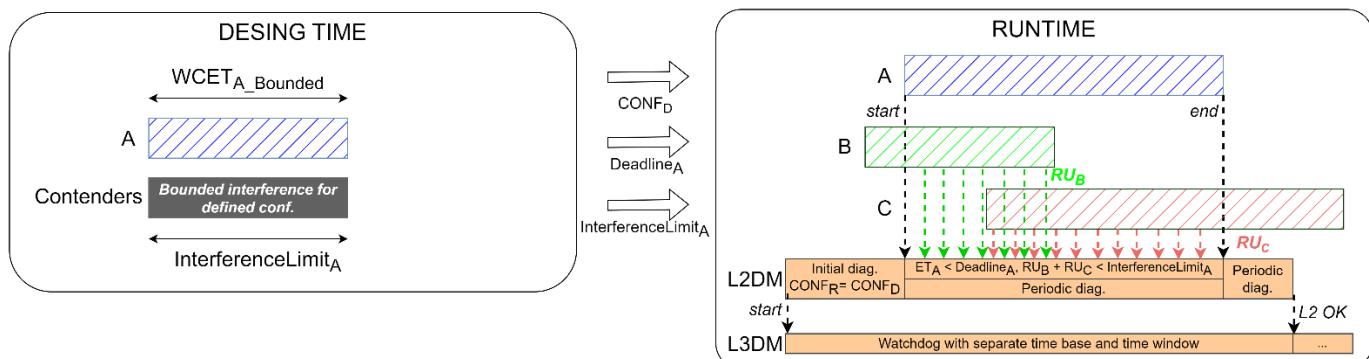

CAST-32A / AMC-20-193 focus on multicore processors and therefore mostly on the hardware computing element and allocation of resources to deal with interferences. The following main risk factors are considered:

- Contention for resources and interference between software applications or tasks even if there is no explicit data sharing among concurrent tasks, low level resources are shared (cache or interconnects) coupling exists on the platform level, which can cause interference between them.

- Interference caused by the arbitration of shared resources.

- Verification of the use of shared resources: demonstrate that the hosted software applications function correctly and have sufficient time to execute in the presence of the interference that occurs when all the hosted software is executing on a multicore. The WCET of a software component or task may increase significantly when other software components or tasks are executing in parallel on the other cores.

- Exceedance of resource capabilities by software applications.

- Hardware dynamic features that can alter system behaviour (energy saving features, clock enable / gating, frequency adaptations, deactivating one or more cores, or dynamic control of peripheral access).

- Configuration settings: active cores, execution frequencies, priorities and allocation of shared resources (memory, cache, interconnect).

### 2.1.3. AI and FUSA Technical Reports (ISO/IEC TR 5469)

As previously stated, ISO/IEC TR 5469 refers to traditional functional safety standards for application independent AI technology elements, and defines the following 6 properties for AI application dependent ones:

- Degree of automation and control

- Degree of decision transparency and explainability

- Environmental complexity and vagueness of specifications

- Operational Design Domain (ODD) complexity

- ODD specification

- Environmental changes: Data drift (training data does not match runtime domain), Concept drift (statistical properties of data change over time)

- Adversarial inputs

- AI Hardware issues

- Technological maturity

### 2.1.4. Safety of The Intended Functionality (SOTIF) (ISO/DIS 21448)

With the increase of advanced functionalities and automation, ISO/DIS 21448 acknowledges that many hazards are not covered by functional safety standards and defines the concept of functional insufficiencies, which can happen even when the system is free from systematic and random faults addressed in functional safety standards. Functional insufficiencies, which could be considered as a type of systematic faults, are defined as one of the following:

- Insufficiency of specification: This mainly affects to the AI lifecycle as it is defined as “specification, possibly incomplete, contributing to either a hazardous behaviour or an inability to prevent or detect and mitigate a reasonably foreseeable indirect misuse”.

- Performance insufficiency: “limitation of the technical capability contributing to a hazardous behaviour or inability to prevent or detect and mitigate reasonably foreseeable indirect misuse”.

### 2.1.5. Summary of risk factors

Table 1 summarises the risk factors described within Section 2.1 mapping them to the affected AI-technology elements the source of information.

Table 1: Summary of risk factors

| Risk factor                                         | AI technology element                                                                                             | Source                                                          |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| Traditional FUSA risk factors (systematic / random) | All AI technology elements (i.e., computational hardware, OS / middleware, libraries, ML framework and ML model). | IEC 61508 and derived FUSA standards (ISO 26262, EN 5012x, ...) |

| HPEC platform integration risk factors              | Computational hardware and lower-level SW (i.e., OS / middleware).                                                | CAST-32A / AMC-20-193<br>ISO 26262 part 11                      |

| AI performance insufficiency                        | ML model or framework.                                                                                            | ISO/DIS 21448 (SOTIF)                                           |

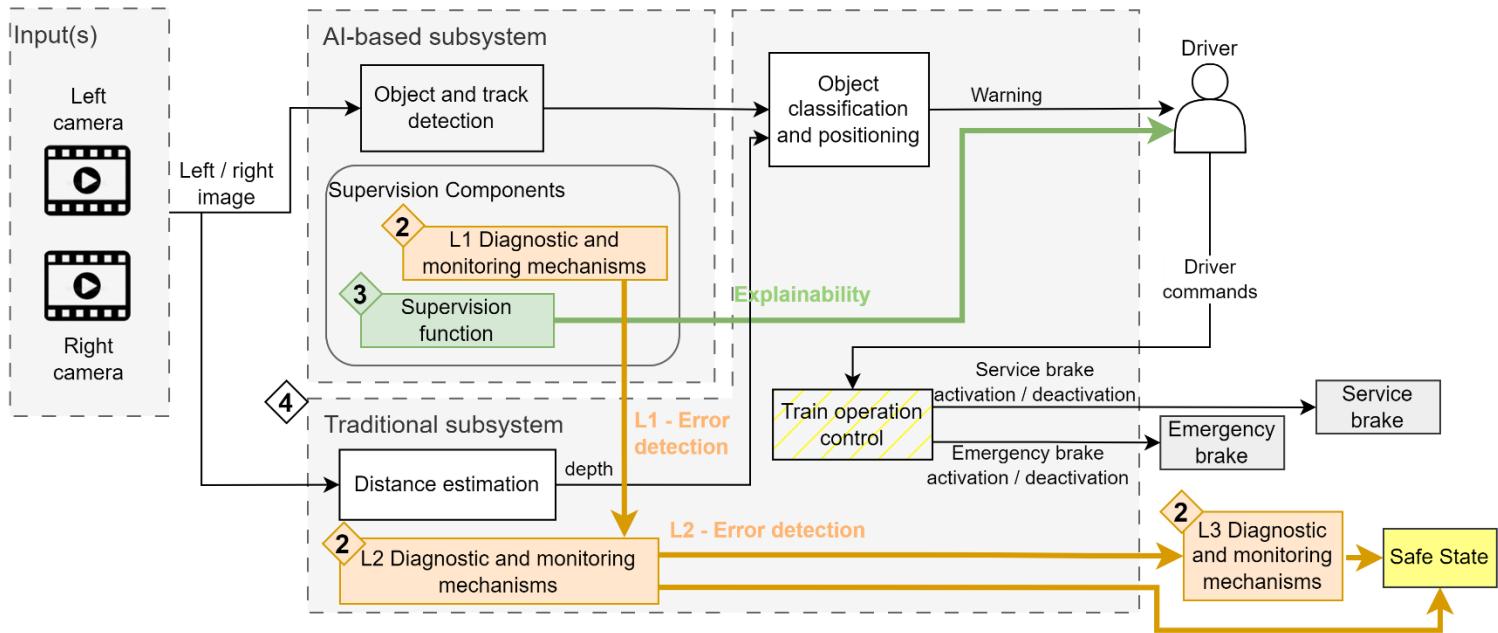

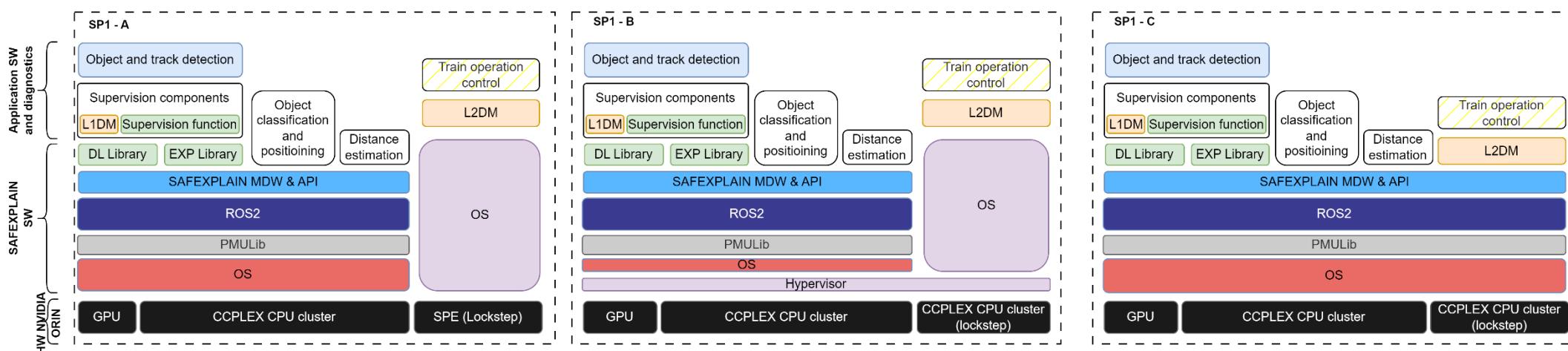

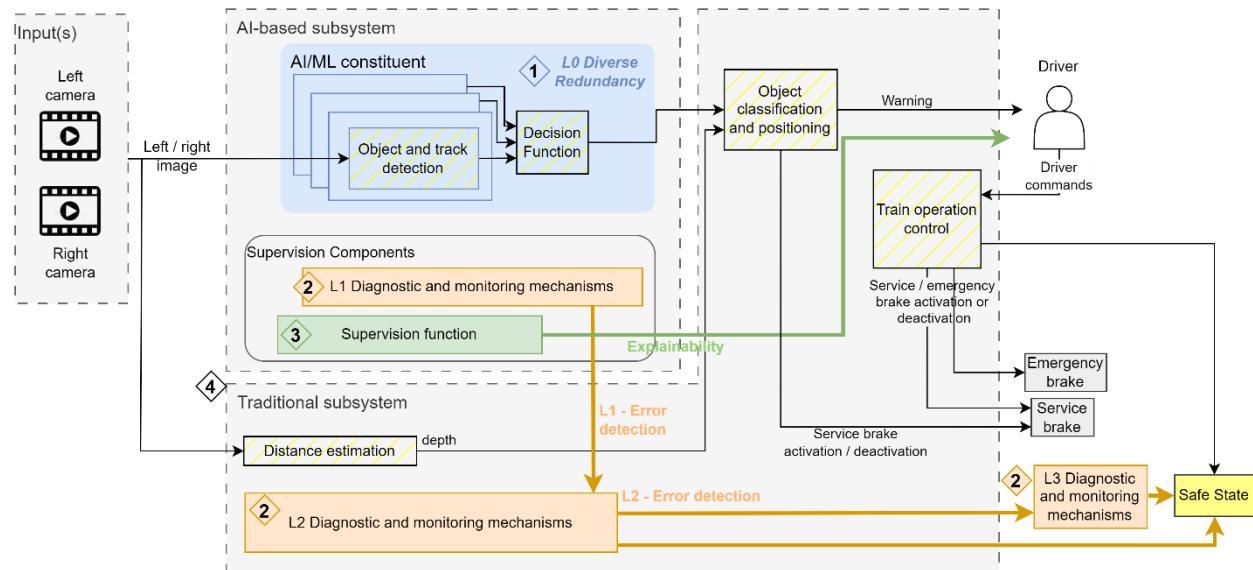

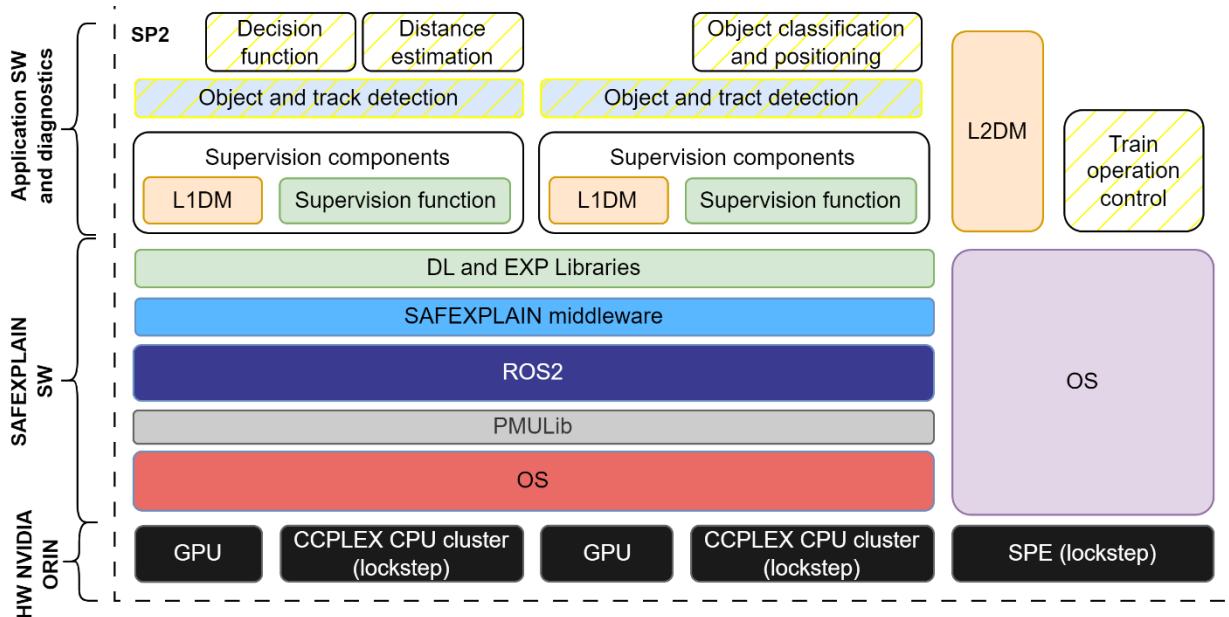

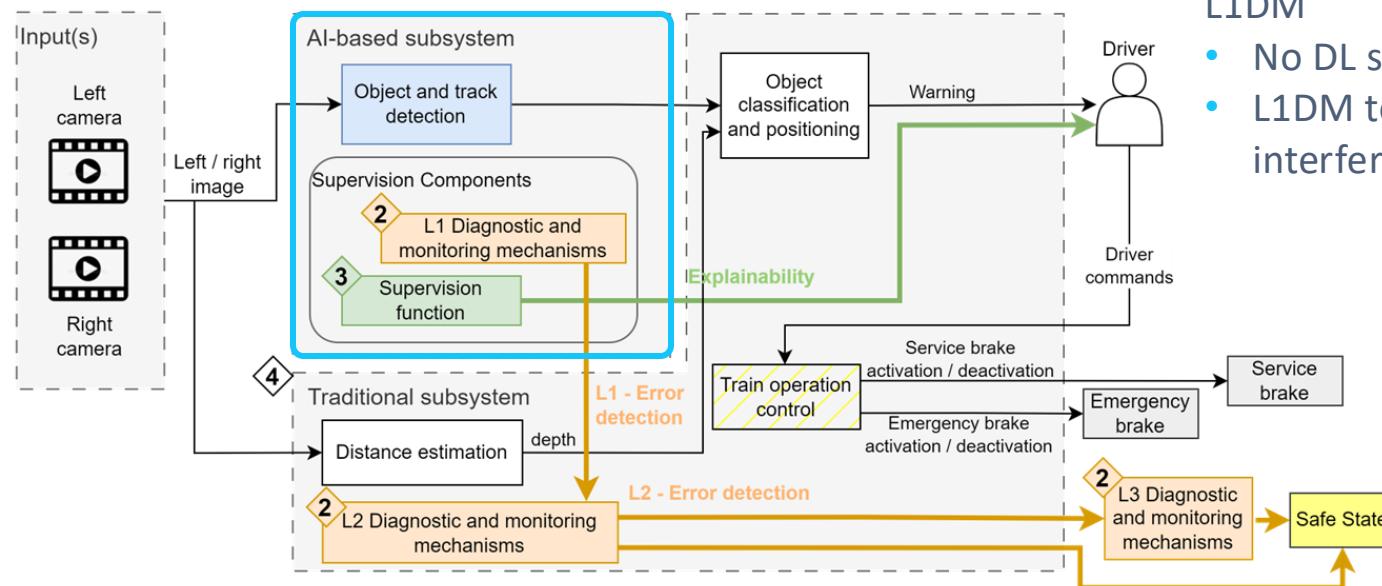

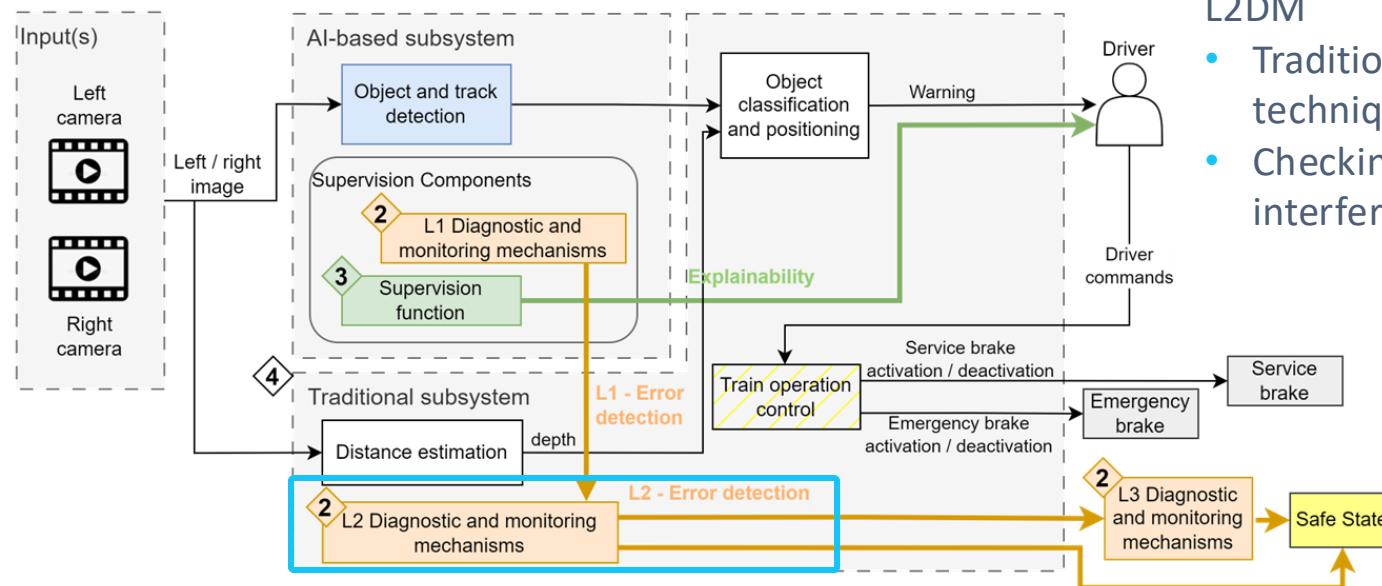

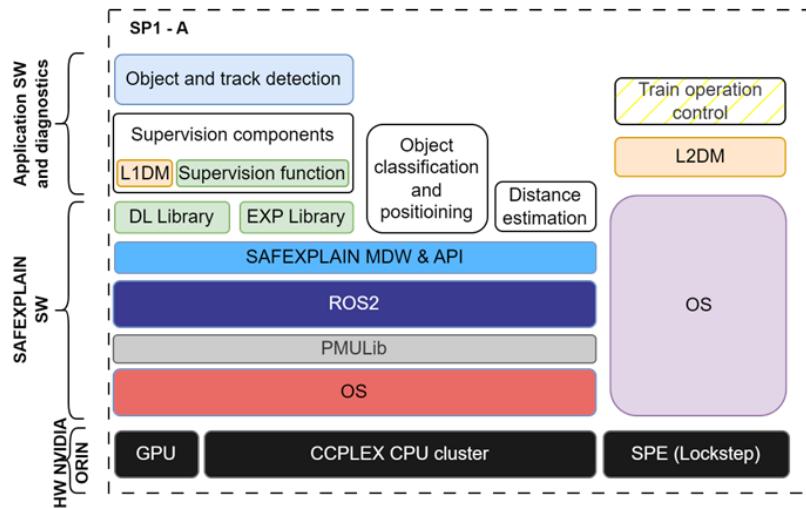

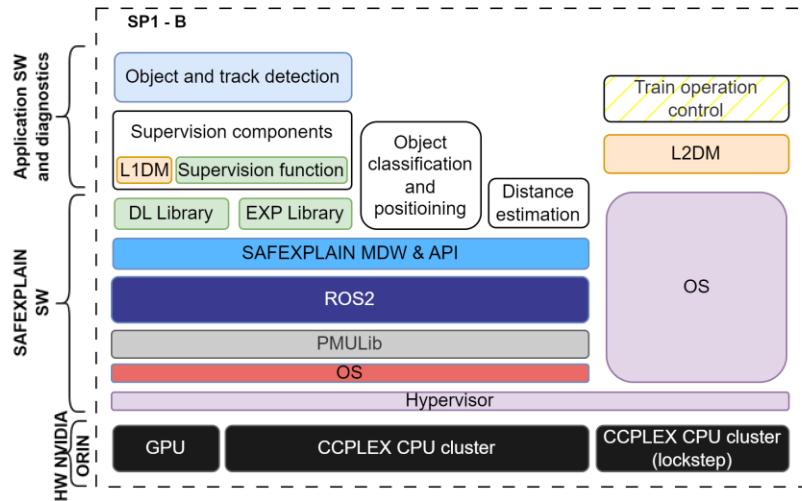

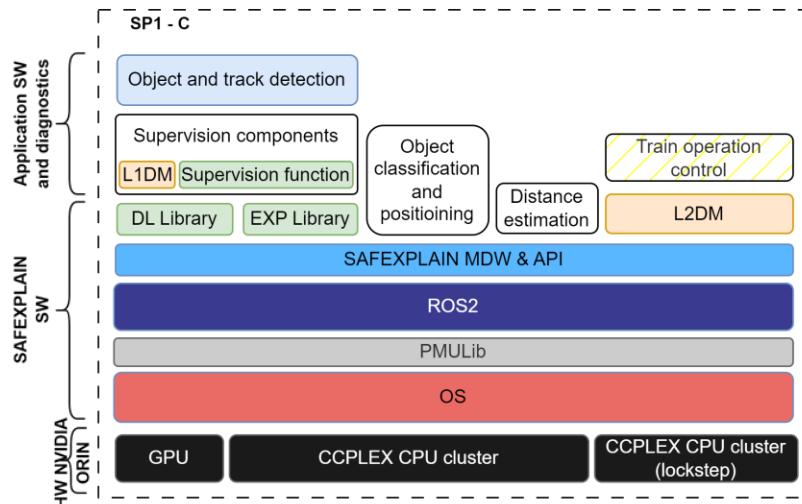

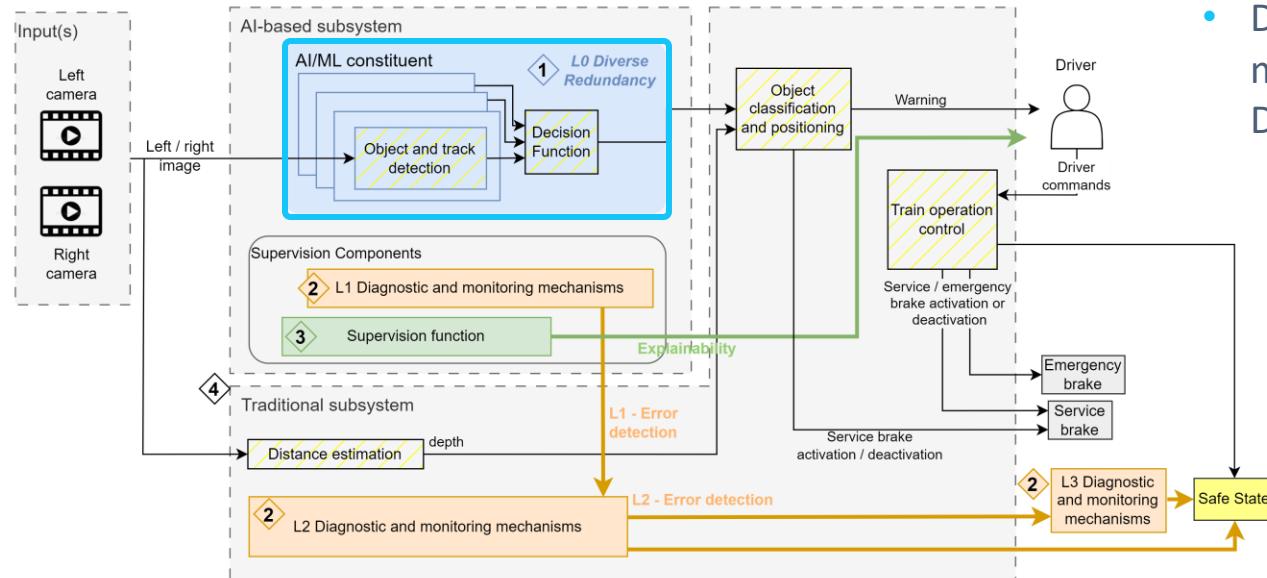

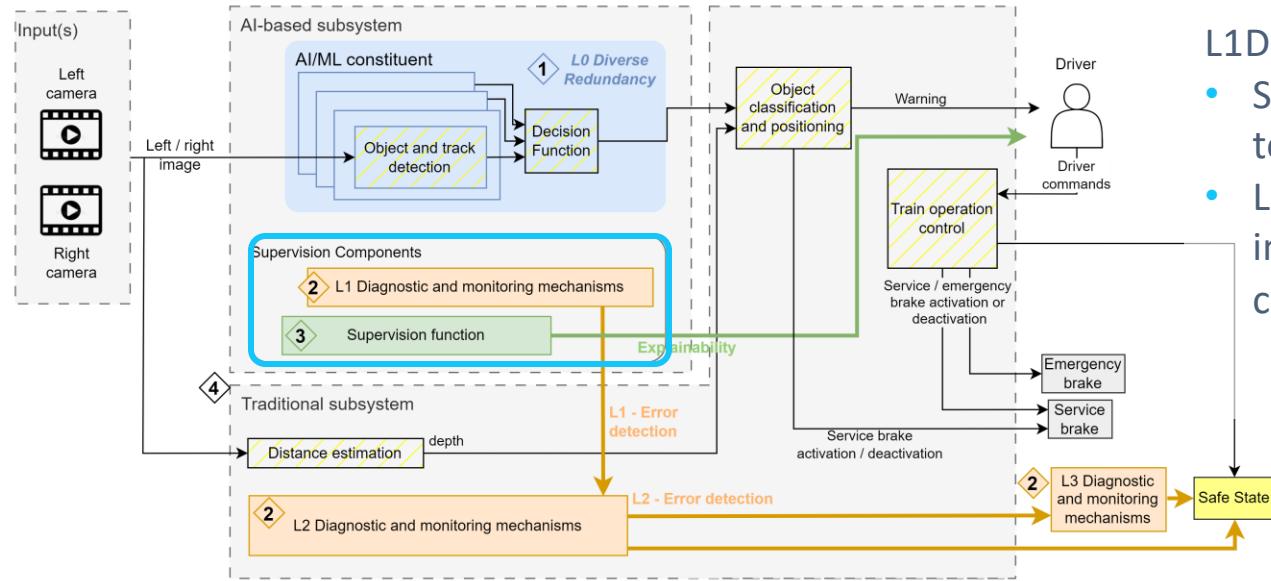

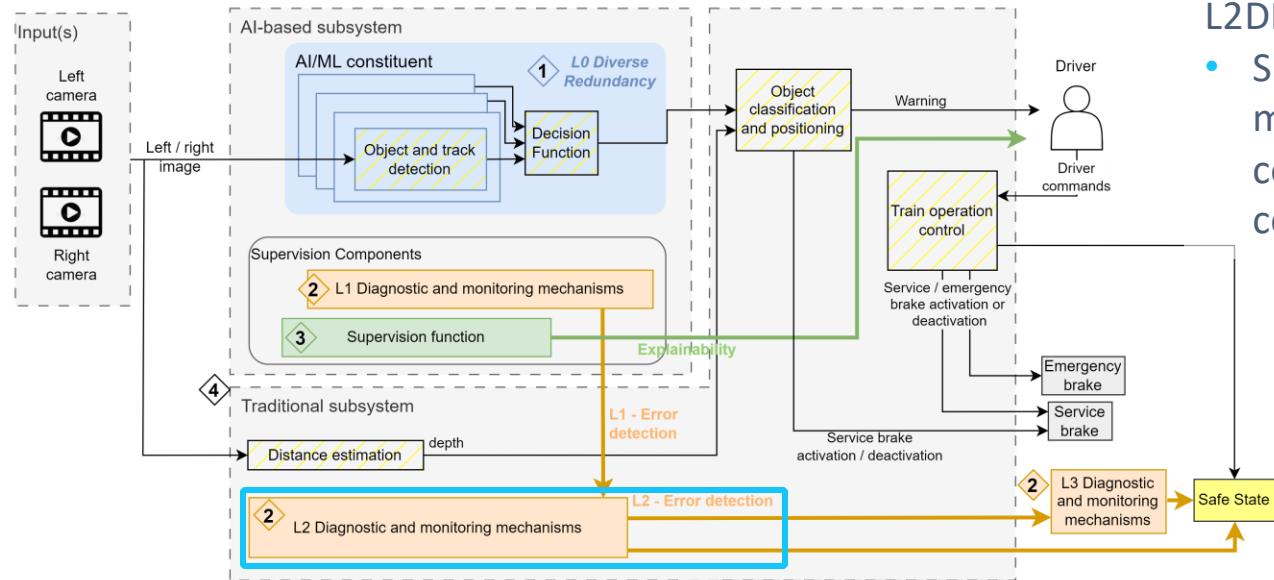

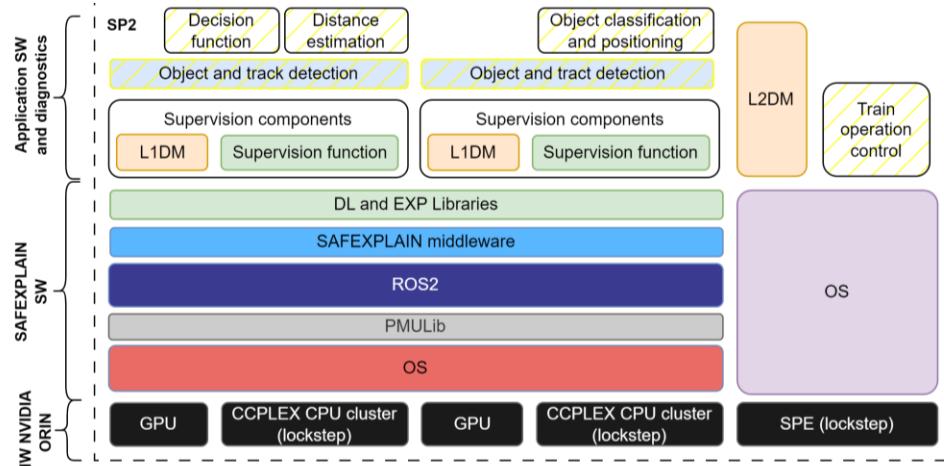

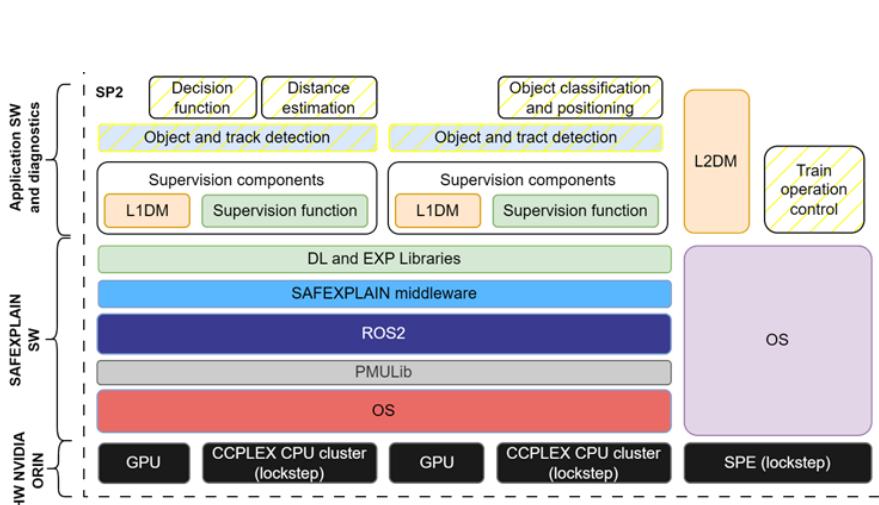

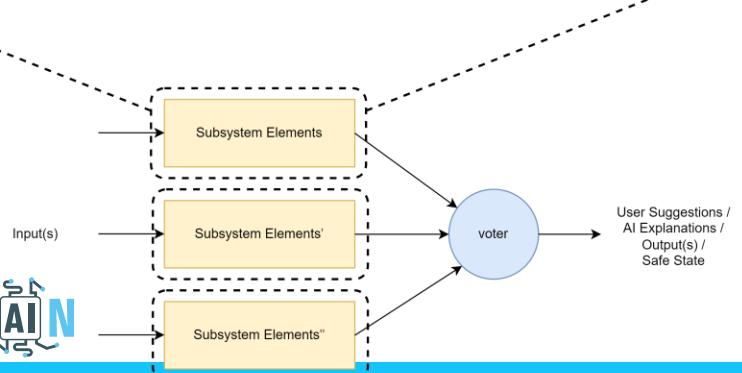

| AI & FUSA risk factors (low/medium integrity level) | All AI technology elements (i.e., computational hardware, OS / middleware, libraries, ML framework and ML model). | AI and FUSA Technical Reports (ISO/IEC TR 5469)                 |