SAFEXPLAIN partners shared key projects results at the 2025 28th Euromicro Conference Series on Digital System Design (DSD). Two papers were accepted to the conference proceedings and presented on 10 and 11 September 2025 by Francisco J. Cazorla from the Barcelona Supercomputing Center and Javier Fernández Muñoz from IKERLAN.

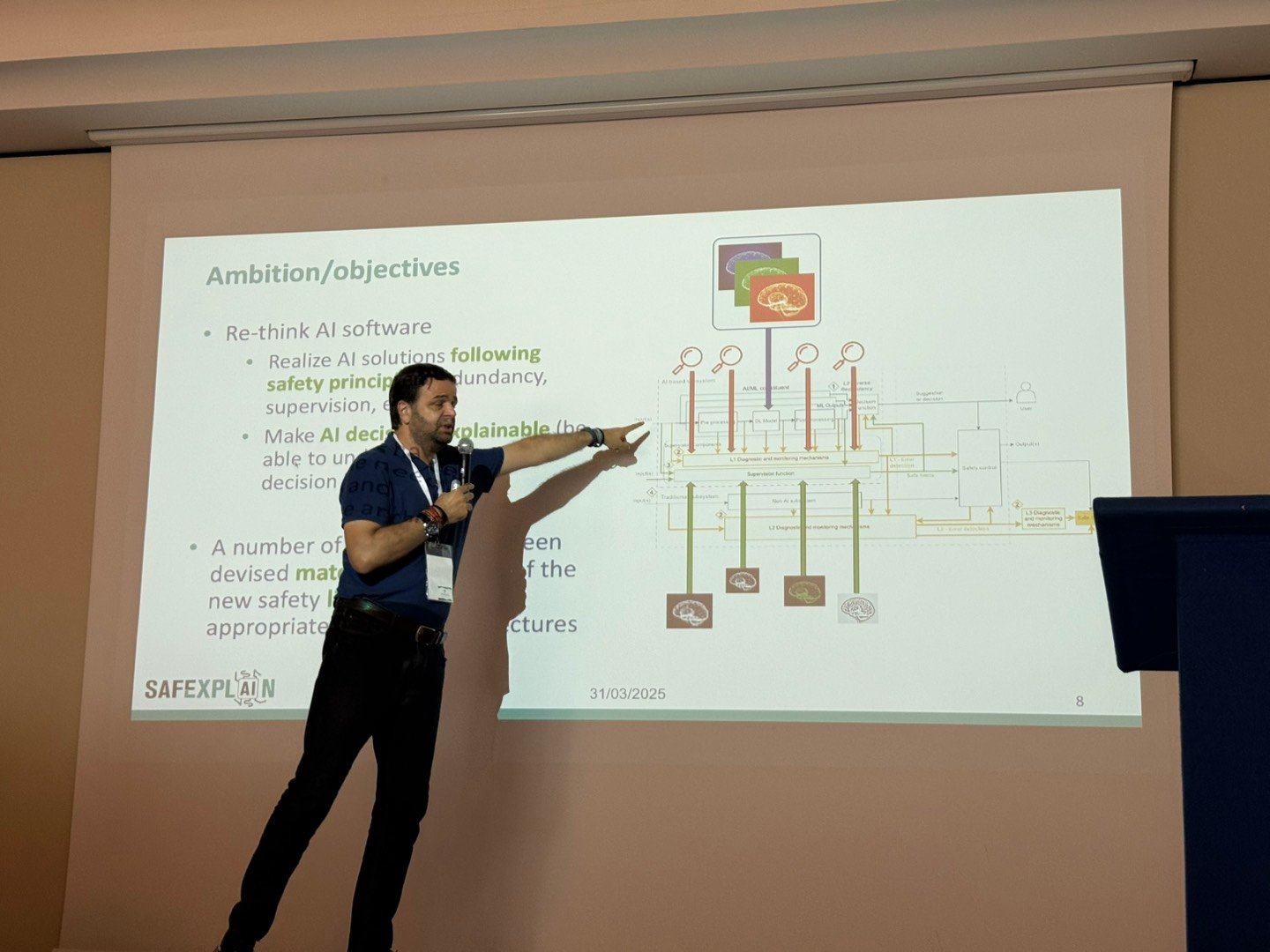

Francisco J. Cazorla’s presentation was based on the paper “SAFEXPLAIN: a Complete Approach Towards Trustworthy AI-Based Safety-Critical Systems,” by Jaume Abella, Irune Agirre, Thanh Bui, Frank Geujen, Gabriele Giordana, Carlo Donzella, Francisco J. Cazorla, Enrico Mezzetti, Axel Brando, Javier Fernández, Irune Yarza, Joanes Plazaola, Robert Lowe, Maria Ulan, Rob Lavreysen, Lucas Tosi, Ilaria Bloise, Lorenzo Feruglio, Ilaria Cinelli, Stefano Lodico, William Guarienti, Giuseppe Nicosia, Valeria Dallara . The presentation summarized the work carried out by the SAFEXPLAIN project during the last three years, with a specific focus on the logic behind AI software design.

Javier Fernández Muñoz presented on behalf of the work done by IKERLAN in the framework of the SAFEXPLAIN project. The presentation was based on the paper, “Towards a Safe End-to-End AI framework: MISRA C-Compliant YOLO for Object Detection” Javier Fernández, Irune Agirre, Irune Yarza, Jon Perez-Cerrolaza. It demonstrated the feasibility of a MISRA C compliance and static memory allocated version of the YOLO framework.

About DSD

The Euromicro Conference on Digital System Design (DSD) addresses all aspects of (embedded, pervasive and high-performance) digital and mixed HW/SW system development and covers the entire design process from specification to microarchitectures, digital circuits and VLSI implementations.

It is a forum for researchers and engineers from academia and industry working on advanced research, development and applications. It focuses on the current and future challenges of: advanced embedded, high-performance and cyber-physical applications; system and processor architectures for embedded and high performance HW/SW systems; design methodology and design automation for all design levels of embedded, high performance and cyber-physical systems; modern implementation technologies ranging from full-custom circuits in nanometer technology nodes to FPGAs and MPSoC infrastructures.