On 11 February, 2025, Dr Enrico Mezzetti, Established Researcher at the Barcelona Supercomputing Center, shared the innovative SAFEXPLAIN platform and toolset supporting the development, execution and analysis of the solutions proposed as part of the project and deployed through the SAFEXPLAIN case studies. In his presentation “Putting it together: The SAFEXPLAIN platform and toolsets”, he synthesized the relationship behind the project’s AI-Functional Safety Management (AI-FSM) Methodology and explainable (XAI) methodologies explored in the first two webinars of the SAFEXPLAIN webinar series.

Project coordinator, Dr Jaume Abella, High Performance Embedded Systems Laboratory Director from the Barcelona Supercomputing Center, opened the webinar with a presentation of the context in which the project is being developed and the motivation for the platform and toolset support.

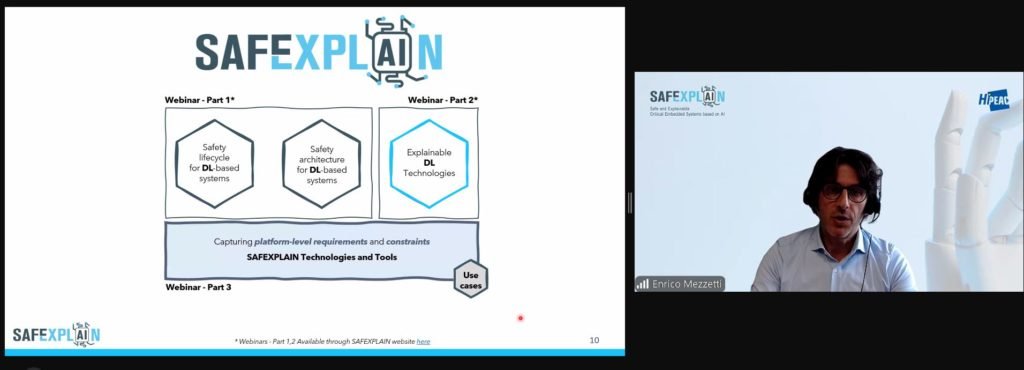

SAFEXPLAIN Platform: Technologies and tools

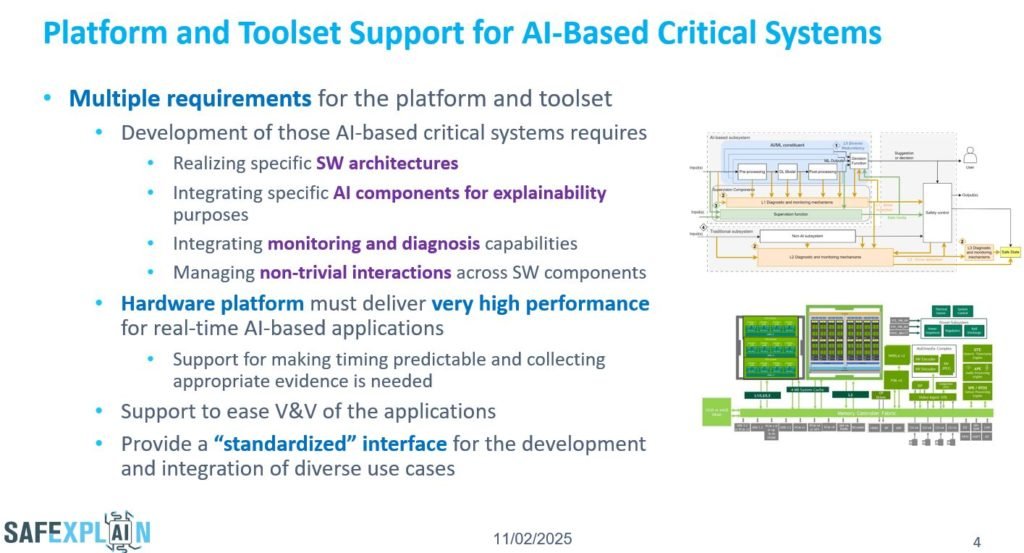

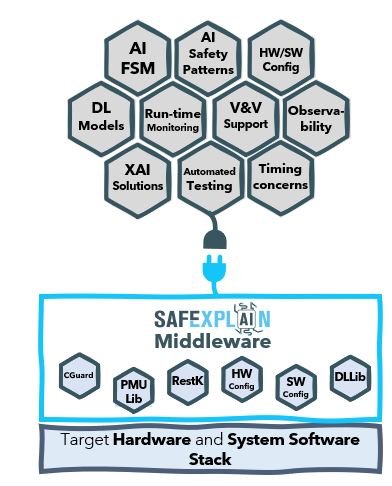

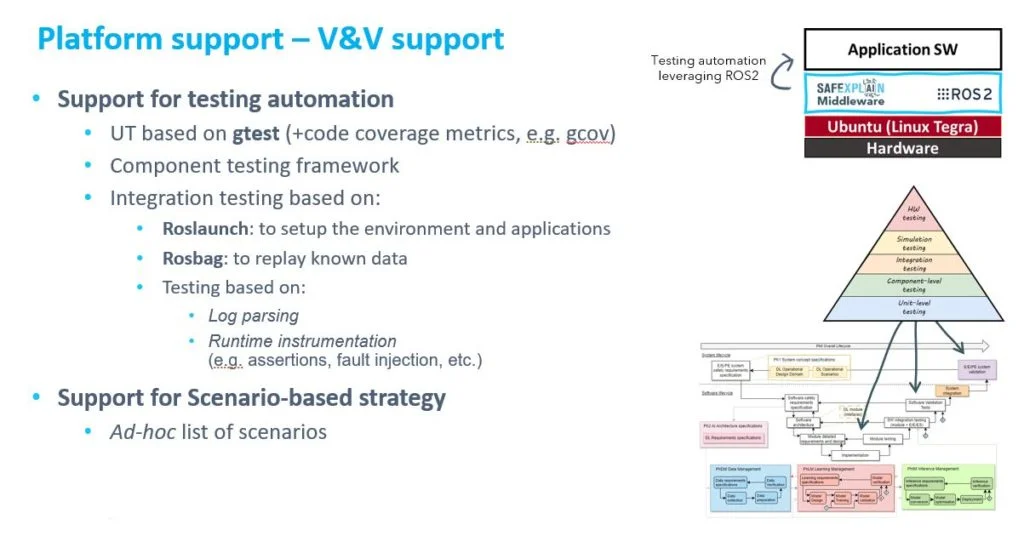

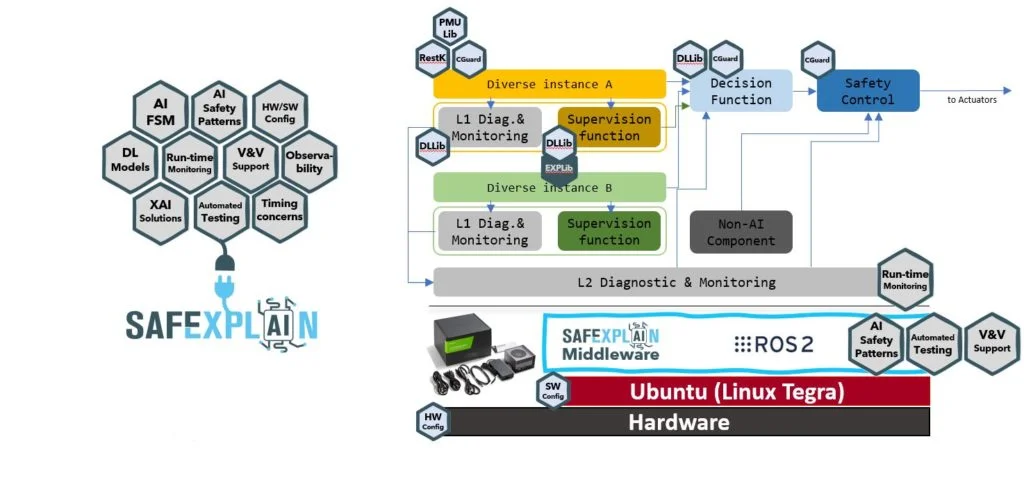

Enrico then introduced the diverse set of platform-level objectives captured by the infrastructure, including support for hardware integration of proposed solutions, a common layer for software verification and validation and functional safety mechanisms, as well as an abstraction layer for system configuration and a reference common stack for the three case studies.

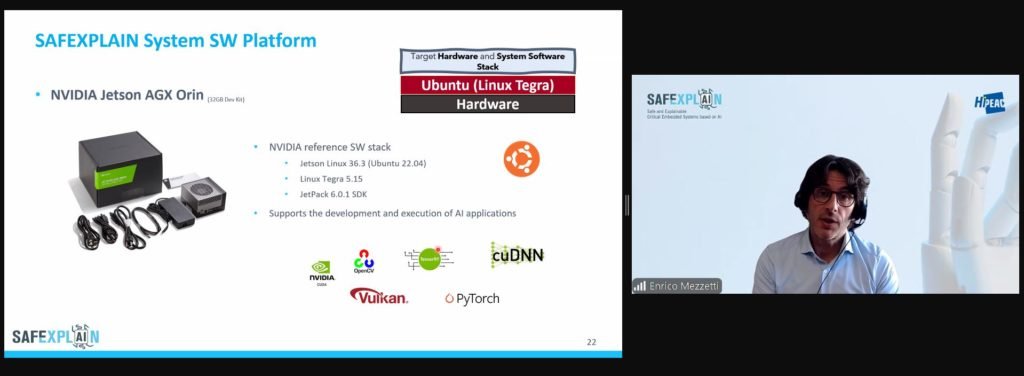

He further highlighted the role of the SAFEXPLAIN infrastructure in contributing to trustworthy solutions that emphasize portability, modularity, and adaptability. An introduction of the project’s hardware and software platforms and middleware set the basis for describing the different aspects of platform support.

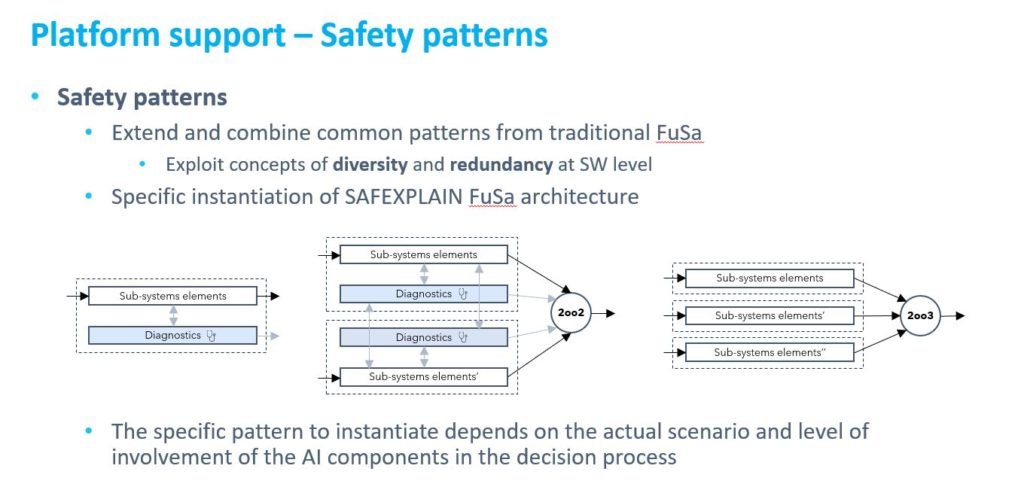

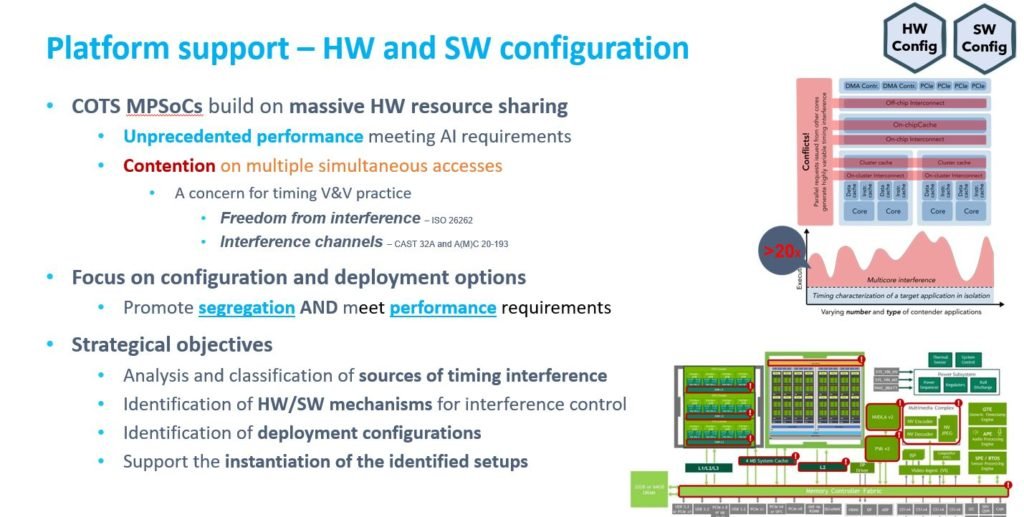

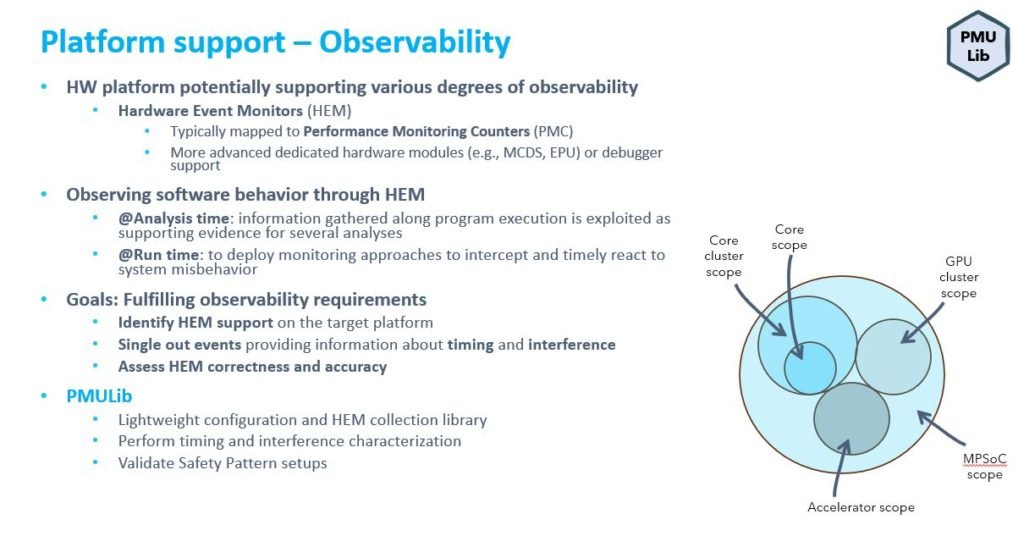

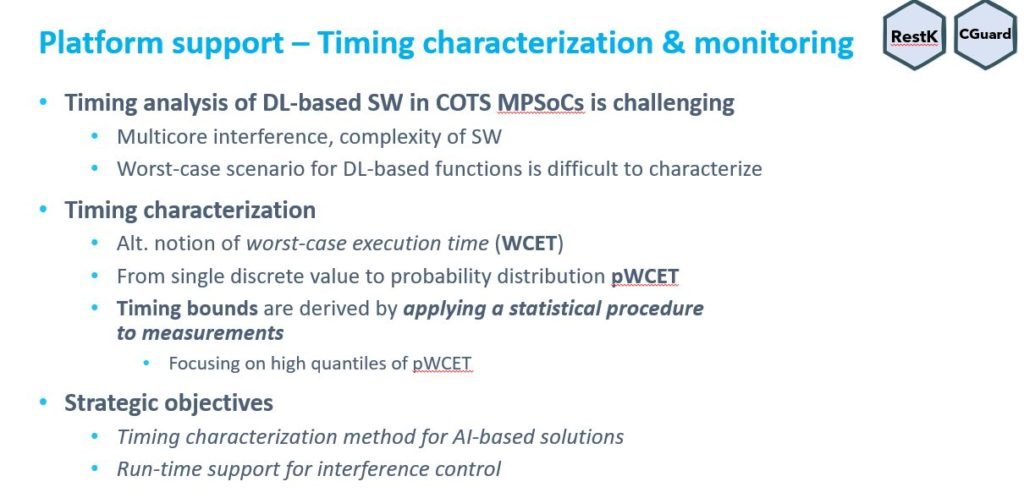

Key platform support features described included:

Enrico concluded with an overview of the platform support, bringing the presentation full circle by highlighting the integration of the different components being developed in the project.

Missed the webinar?

Watch the first two webinars in the series

Resources

Learn more about the speaker

Dr Enrico Mezzetti has been an Established Researcher at the Barcelona Supercomputing Center since 2016. He holds a PhD in Computer Science from University of Bologna (Italy) on software timing analysis and industrial development process. He authored more than 60 publications on the verification of critical embedded systems, specializing in timing characterization and analysis of multicore systems, RTOS, and software architectures.